SoC设计链中的可配置IP

确性和吞吐量方面的验证。如果IP运用于商业系统,则该IP必须提供与常用的总线结构和外围控制器的接口。对于片上和片外存储的接口而言就更加重要了,因为在典型的数据驱动应用中,媒体和图像处理、设备的性能和功耗等都受控于内存访问的效率。

为了满足这些要求,Improv的Jazz体系结构提供了一系列的集成模块或是iBlock,这样就可以根据具体需求进行选择并将其集成为Jazz处理器配置的一部分。这些模块都是预先设计并通过验证以确保能与常用的总线和存储控制器相结合,从而基本上无需进行重新设计就能很轻松地将IP嵌入到当前的SoC设计中。

主机总线接口(HBI)单元是一个灵活的模块,很多年来一直运用于众多的总线结构中。但是,因为基于ARM的AMBA和AIX总线结构颇受欢迎,所以该HBI单元就专为这种应用进行了高度优化,不需要做任何修改就可稳定可靠地运用于多数的SOC 中。

数字通信接口(DCI)单元同样也能提供一个灵活和具有鲁棒性的接口,以连接常用的内存控制器。同时,该单元也能灵活地运用于其他任何控制器中,所以我们的设计和验证大都致力于面向众多流行的控制器,也就是Denali的Databahn系统。内存控制器和物理实现是商业系统的底层设计中实现时序要求最具难度又最重要的部分。在高清电视和高频宽带卫星通信系统等应用中,这方面的要求愈发重要。在众多的系统验证中,DCI都成功通过了测试,证明了我们在该系统单元设计中花费的时间和精力是有效的,同时为用户构建自己的系统提供了有力的支持。

6、自动配置和验证

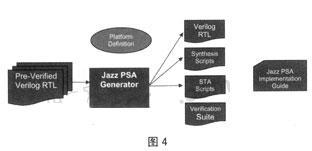

一个复杂的可配置IP只有符合Jazz标准并能被授权使用的工具进行综合开发时,它才能得到最有效的利用。通过XML数据库,配置流程将直接自动监测由先进的自测试组件和系统物理设计所需的脚本所产生的结果。Composer工具提供图形拖放窗口进行处理器或平台的配置。 面向任务的软件方法结合了自动配置功能,将软件和硬件的开发流程分离开来以使它们实现并行工作。Com-poser为配置生成了一个XML数据库,生成器就是利用该数据库使下游的设计流程实现自动配置。

JazzPSA Generator是利用为平台自动产生的配置数据转换针对终端FDA工具生成脚本。

7、成本/性能指标

可编程和数据流可配置处理器相对于硬线系统而言是一个非常显著的优势,因为一个设计就能运用于多种不同的应用,而且只需稍加编译和重新配置就可生成一系列特殊应用处理器。但是,如果在性能,功耗或是芯片面积上已经存在巨额管理费用,则该优势还是不太可成为净增益点。

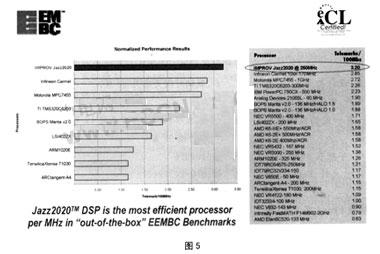

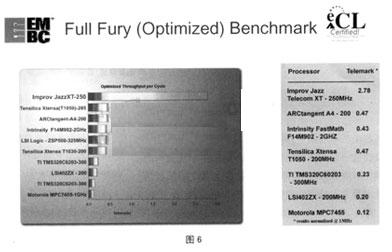

Improv的Jazz系统已经在实际芯片中得到验证,同时也得到一些独立的基准测试服务机构的高度评价,他们认为可配置的处理器远比固定可编程设计或是硬连线设计的效率高得多。以下图表就是由:EEMBC组织(http://www.EEMBCorg)根据其提出的一系列基准,将.Jazz处理器和其他运行电信相关的测试流的商业系统进行比较后的分析结果。该结果显示azz处理器因为出人意料的巨大优势(未经修改)而脱颖而出,若是采用了Jazz体系结构的可配置性,那这个优势就更为突出了。

8、结论

选择可配置IP作为SoC设计链的一部分,已经被证实是提高产出能力的重要资产因素。为了实现提高生产率的期望,可配置IP就必须满足文章中提及的这一系列苛刻的要求,借助Improv系统公司的领先解决方案,工程师可以在成本、性能、功耗、灵活性以及上市时间等多个方面占得先机。

- LCoS(硅基液晶)显示屏设计与应用(08-27)

- 系统级芯片发展之路依然任重道远!(11-13)

- 在SoC中集成FlexRay网络控制器的设计策略(01-08)

- 用于便携式多媒体SoC的视频处理方案 (02-09)

- H.264音视频编解码SoC芯片Hi3510的原理和应用 (02-22)

- 数字视频系统设计中的集成新概念 (07-22)