在SoC中集成FlexRay网络控制器的设计策略

为了使先进的汽车应用如线刹和稳定性控制成为可能,业内建立了新的标准FlexRay以提高车载网络的数据率、可靠性和安全性。FlexRay联盟经过5年工作之后,终于将规范稳定下来。标准组件已经上市,第一辆装备FlexRay的汽车有望在今年末量产

随着FlexRay开始进入实用,现在是汽车电子工程师计划在其设计中添加FlexRay的时候了。对于那些想把FlexRay集成到新型芯片的公司,现在已经可以获取可综合、经过验证的FlexRay知识产权(IP)。

新的汽车应用如先进引擎和排放控制及线控功能需要许多电子组件,其中每一个都对更高的数据率、确定性的行为和可靠性有强烈的要求。这就极大地增加了对汽车总线的要求,而FlexRay通信协议的开发正是为了满足这些要求。

FlexRay技术可以被分为三个主要领域:配置和管理FlexRay簇的软件、实现FlexRay协议的数字逻辑及模拟信号驱动器。在此,我们重点讨论FlexRay IP的数字硬件单元并考虑如何将其集成到系统级芯片(SoC)之中。

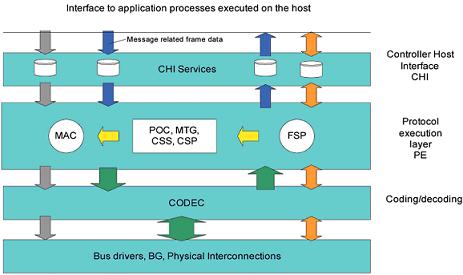

如上所示,FlexRay层级的中间层是协议执行层,在此流出的帧数据被发送到物理层。在一侧,协议执行层与控制器主接口对接,其中包含所有接口数据的存储并给控制器主接口提供服务。在另一侧,协议执行层与编码/解码层对接。物理层包含总线驱动器、总线监护选件和物理互连。

如上所示,FlexRay层级的中间层是协议执行层,在此流出的帧数据被发送到物理层。在一侧,协议执行层与控制器主接口对接,其中包含所有接口数据的存储并给控制器主接口提供服务。在另一侧,协议执行层与编码/解码层对接。物理层包含总线驱动器、总线监护选件和物理互连。

概念的最佳分割

在设计FlexRay核的过程中,设计工程师应该把重点放在与通信相关的容错设计,而不是放在诸如消息协议算法之类与应用相关的问题。该范例确保其设计适用于具有不同容错要求的各种应用。

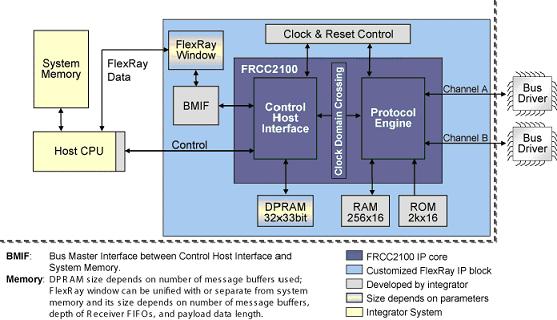

FlexRay核被分为负责处理所有FlexRay特有协议的协议引擎(PE)和负责处理将FlexRay功能集成到其它系统的所有任务的控制器主接口(CHI)。

CHI主要访问FlexRay核的配置、控制和状态寄存器及消息缓冲器的配置、控制和状态寄存器。消息缓冲器具有FlexRay帧(已接收帧和待发送帧),包括帧首、有效载荷及帧状态信息。消息缓冲器数据存储在FlexRay存储器之中,而消息缓冲控制结构在CHI中实现。

终端用户应用需求的差异很大,因此,该内核应该具有可配置能力,以便集成商能够优化应用性能并调节芯片类似面积和功耗之类的特性。例如,在IPextreme提供给飞思卡尔FlexRay控制器核之中,内核可以被配置为实现最大256个消息缓冲器和最大输入均为256的两个接收FIFO。

一些应用可以从用户定制和面向特定应用的CHI获益,这需要良好定义的、详细和备有证明文件的的PE接口。IP供应商提供满足许多应用需求的通用目的CHI,它包括所有详细的FlexRay功能,如独立收发缓冲器(单和双缓冲发送)的使用、状态或事件传输模式、接收FIFO功能、消息缓冲过滤和双通道模式。

然而,特定的应用可能需要这些功能的子集。对于一些面积和功耗很重要的应用,减少CHI复杂性的好处很大。该策略仅当PE模块的接口和行为被非常好地定义和归档时才可行。

时钟域交叉(CDC)单元实现从CHI时钟域到PE时钟域的信号交叉,反之亦然,从而容许异步和CHI时钟域。CHI频率依赖于待处理的消息缓冲器的复杂性和数量,它可以比PE时钟慢很多或快很多。如果CHI可用与PE一样的40MHz时钟驱动,那么,就可以省略CDC以减少门数。

依赖于系统存储器的要求,如规模、反应时间和带宽,保持消息报头和有效载荷的FlexRay存储器窗口可以被存储在系统存储器(顶部)或独立的存储器之中。下图显示了FlexRay核模块图及其与主处理器通信的两种方式:

优化和配置核 参数:硬件参数让集成商能够定制设计以省略不用的硬件。对于FlexRay器件,可能有若干随系统而定的参数,如总线和数据宽度及架构参数,包括消息缓冲器和有效载荷的最大数目。消息缓冲器(4到256个)的最大数目对CHI的面积和时钟要求有很大影响,其频率范围从20到140 MHz。设计者可以选择仅仅实现必需的消息缓冲器,以减轻针对成本、面积和功耗的设计优化工作。 省电:当时分

- LCoS(硅基液晶)显示屏设计与应用(08-27)

- 系统级芯片发展之路依然任重道远!(11-13)

- 用于便携式多媒体SoC的视频处理方案 (02-09)

- H.264音视频编解码SoC芯片Hi3510的原理和应用 (02-22)

- 数字视频系统设计中的集成新概念 (07-22)

- SoC设计链中的可配置IP (10-12)