详解基于CAN总线的汽车仪表系统—芯片选型与电路设计

H128内置一个8路10位线性逐次逼近A/D转换模块,该模块特性如下:

1)10位数字量转换仅需75;

2)采样缓冲放大器

3)可编程采样时间

4)数据左/右对齐方式,无符号/有符号结果

5)外部触发转换通道

6)转换完成中断

7)模拟/数字量复用通道;

8)1一8位顺序转换长度

9)多通道扫描,连续转化模式

A/D模块内部可分为三个部分:IP总线接口、转换模式控制寄存器/寄存器列表、自定义模拟量。IP总线接口负责该模块与总线的连接,实现A/D模块和通用I/O的目的。转换模式控制寄存器列表中有控制该模块的所有寄存器,自定义模拟量负责模拟量到数字量的转换。A/D转换模块没有分频机制,最大转换时钟频率为 ZMHZ,最小转换时钟为5OOKHZ,所以必须是经过分频后的转换始终频率处于两者之间,可能得不到正确的结果。转换时间可用以下公式来计算:

4.1.3串行外设接口SPI

在一个单片机系统中,MCU除了进行控制数据传送外,还需要与外围器件进行数据交换。虽然并行接口传输速率比串行接口要快,但其占用了太多的硬件资源,而且连线复杂。所以为了简化系统,现在各厂家推出的芯片中大多都带有串行数据接口。

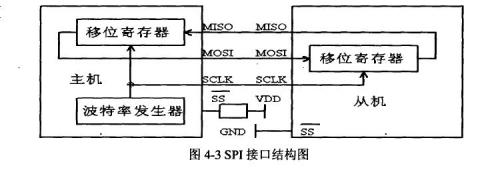

SPI(serialperipheralinterfaee)是一种高速高效率的同步串行技术,这种接口技术主要用于MCU与外部接口芯片交换数据,这在Freesca1e(原Motorola)单片机中已经是一个标准模块,也逐渐成为一种工业接口标准。SPI接口常用于主从分布系统,一个标准的SPI系统包括一个MCU和几个不同的外部设备。SPI使用4条线,具体为:

1)串行时钟线 SCLK(SerialCloCk)。SCLK是主机与从机之间数据传输的同步信号。对于主机来说,SCLK是时钟输出引脚,而对于从机来说,SCLK就是时钟输出引脚。

2)主机输入、从机输出数据线 MISO(masterin/slaveout).MISO是SPI模块的两根串行数据之一,在全双工操作模式下,SPI主机的MISO被连接到从机的MISO,这样,数据由从机传到主机。仅在SPI设备配置成主机模式时,才可以由M工50接受数据。

3)主机输出、从机输入数据线 MOSI(Masterout/slavein)。MOSI是Spl模块的另外一根串行数据线。

4)低电平有效的从机选择线 55(slaveseleet)。55在主机和从机模式中具有不用的功能。从机模式下,SS是依次数据传输开始前允许SPI工作的片选信号;主机模式下,SS可以置位 MODF标志位,保证一个系统只有一个SPI作为主机。SPI工作原理如同一个16位的分布式移位寄存器,一半在单片机里面,一半在外设中。当SPI工作时,通过串行时钟线的同步信号,循环移位8位,从而实现单片机与外设的数据交换。工作原理如图4一3所示:

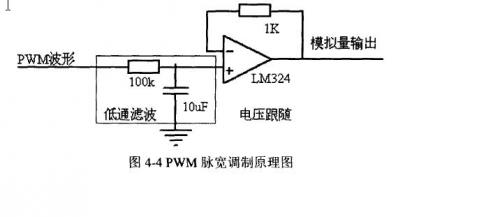

4.1.4PWM脉宽调制模块

PWM(pulsewidthmodulate)即脉宽调制,脉宽调制波是一种可用程序来控制波形占空比、周期、相位的波形。H128单片机内部集成了2路PWM输出通道,在精度要求不高的情况下,PWM模块可以当作单片机的D/A口模块使用,从而降低系统成本Isl]。本系统正是利用了这一特性来改变仪表背光灯的明暗度,其原理如图4一4:

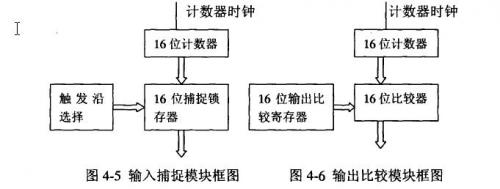

HCs12增强型定时器和HC12定时器一样,有8个输出比较瑜入捕捉通道,通过选择n0s寄存器的Iosx位可以在输出比较和输入捕捉的功能之间切换(见图4一5和图4一6)。

普通输入通道中带有一个捕捉寄存器用来记录管脚上电平变化时自由计数器的锁存值。在带缓冲的输入捕捉通道中,除了带有捕捉寄存器之外,还有一个保持寄存器,可以在不中断的条件下连续记录两次自由计数器的值。脉冲累加器与定时器中4个带缓冲的通道相连,通过检测相应管脚上的有效边缘来记录脉冲的个数。相邻的两个8位脉冲累加计数器可以联成为一个16位的脉冲计数器,用户可以选择4个8位或者2个16位累加计数器。定时器最常见的用法是用于内部定时和外部脉冲计数,脉冲累加器有两种工作模式:锁存方式和队列方式。

锁存方式:当模数计数器减为0、向模数计数器写入$仪刃0或写强制锁存位ICLA时,脉冲累加计数器将锁存到相应通道的保持寄存器中,并将累加计数器清零。

队列方式:当读取某通道保持寄存器的值时,相应的脉冲累加器的值将被写入该保持寄存器中并将脉冲累加器清零。

4.1.6.LCD接口模块

H128内部带有笔段式LCD驱动模块,可以驱动32个前极和4个背极,所有产生的波形均由片内的充电泵提供,不需采用外部元器件脚l。有4个1/0端口BPO一BP3专门用来驱动背极,其他32个前极驱动引脚为复用端口,从FPO一FP27,PT4一PT7。当LCD驱动模块禁止时,LCD显示将被关闭,所有的前极和后极驱动电压都为VDD,梯形电阻结构也将不在和VDD相连,以此来降低功耗。一般根据需要多少背极驱动来设置LCD输出波形的占空比,可以有

- 胎压监测系统(TPMS)技术与设计考虑(11-26)

- 利用先进的MCU技术实现电机高效率控制(01-10)

- 基于MCU和DSP的步进电机控制技术(01-10)

- 车载液晶电视/显示器专用MCU及设计方案(01-11)

- 用MCU来控制蓝牙GPS模块 (07-06)

- 如何解决汽车车身控制设计的三大挑战 (09-29)