嵌入式车牌识别系统的设计及实现

1、引言

随着我国国民经济的高速发展,国内高速公路、城市道路、停车场建设越来越多,对交通控制、安全管理的要求也日益提高,智能交通系统(Intelligent Transportation Systems,简称ITS)已成为当前交通管理发展的主要方向,而车牌识别(License Plate Recognition,简称LPR)系统技术作为智能交通系统的核心,起着举足轻重的作用,它在高速公路、城市道路和停车场等项目管理中占有无可取代的重要地位[1-2]。

本文所研究的车牌识别系统,正是在这样的背景下提出来的,对于目前LPR作为ITS中的核心关键技术,具有相当大的理论和现实意义。本系统所设计的是一个基于DSP和FPGA的嵌入式车牌识别系统[3-4],该系统不同于传统的车牌识别系统,具体实现过程将在下文详细描述。

2、系统结构设计

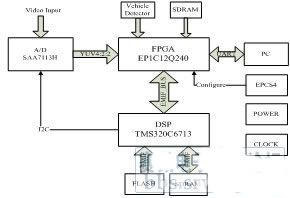

传统的车牌识别系统主要采用摄像头、视频采集卡、工控机几个主要模块搭建出来的方法来实现,其优势是实现容易,但是成本高、实时性不强、安装和维护不便。而在本文系统设计中,摒弃了传统的模式,采用TI公司的TMS320C6713B高性能(强大的并行运算能力)DSP作为识别算法的运行硬件平台,Altera公司性价比很高的Cyclone系列EP1C12Q240型号的FPGA作为协调整个系统的工作与相关的图像采集及控制,再加上一些外围器件(FLASH、SDRAM等)共同构成本嵌入式车牌识别系统硬件平台,如图1所示。

与传统的车牌识别系统不同,该系统无需计算机即可实现车牌图像的采集、识别、输出结果,具有识别性能高、环境适应性强、安装维护简单、成本低等特点。其中采用以DSP和FPGA作为核心的系统设计最大优点是结构灵活、通用性强、适合于模块化设计,从而能够实现高效率的算法和实时控制;同时其开发过程可以并行进行。

图1 车牌识别硬件框图

2.1 视频输入模块

目前,世界上实际应用的电视信号制式主要有NTSC制、PAL制和SECAM制3种,世界上大多数国家采用PAL制,我国也采用PAL制,此系统采用的摄像头输出的视频信号就是标准的PAL制式。

PAL电视制式规定,场扫描频率为50Hz,每秒扫描25帧图像,每帧包括奇、偶两场图像,每帧图像的扫描行数为625行。电视信号由"图像信号"和确保同步的"复合同步信号"以及消除扫描逆程回扫线的"复合消隐信号"等辅助信号构成。PAL制电视信号转化为数字视频信号后,一般输出数据格式符合ITU656 YUV4:2:2标准,输出一帧图像的625行数据中,其中有效图像数据占572行,其他为场消隐信号;同样,每行有效的图像数据也只有720个象素。

本系统中输入是PAL制式的模拟图像数据,必须要经过A/D转换才能供后续系统处理。此系统选用的视频解码芯片(A/D)是Philips公司的SAA7113H[5],支持标准的PAL制式视频信号输入。输入可以为4路CVBS或2路S视频(Y/C)信号,通过内部寄存器的不同配置可以对输入进行转换,输出8位"VPO"总线及一些场、行同步控制信号,其中输出图像数据为标准的ITU656 YUV4:2:2格式。SAA7113H内部具有一系列寄存器,可以配置为不同的参数,对色度、亮度等的控制都是通过对相应寄存器改写不同的值,寄存器的读写需要通过I2C总线进行。由于TMS320C6713有自带的I2C总线接口,所以系统设计里,利用DSP通过I2C总线对SAA7113H进行配置控制,简易了系统的设计[6]。

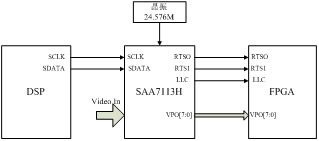

SAA7113H的VPO[7:0]总线以及RTS0、RTS1、LLCLK与FPGA相连,通过DSP的I2C总线把其中的RTS1、RTS0分别配置成场、行同步信号,只有在行场同步信号都同时有效时,才是有效的图像数据输出,否则一般为图像的消隐信号。此时我们只要根据LLC时钟来对VPO总线上的数据来采集即可得到完整的图像数据(720*572大小)。SAA7113H与DSP和FPGA的连接方式如图2所示。

图2 SAA7113H与DSP和FPGA的连接示意图

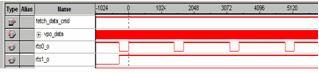

经过实际操作,通过DSP的I2C总线对其进行正确配置,然后由Verilog编写的FPGA程序来进行图像数据的采样,再用Quartus II自带的SignalTap II Logic Analyzer(逻辑分析仪)对波形进行相应的分析,验证了系统中一些重要的信号,结果显示是正确可行的。图3显示的行、场同步信号RTS0、RTS1与VPO数据输出的关系,达到了预期的结果。

图3 行场同步信号(RTS0、RTS1)及VPO波形

2.2 DSP功能模块

DSP作为本系统的核心芯片,主要有两方面的关键技术:一是DSP硬件平台的搭建;二是DSP程序的开发,包括DSP的算法移植及底层驱动编写。

2.2.1 DSP硬件搭建

TMS320C6713B是TI公司的一款高性能的32位浮点DSP[7]。其工作频率最高可达300MHz,每秒可执行2400MIPS和1800MFLOPS,非常适合在大数据量的图像处理场合中使用。集成了丰富的片上外设,包括PLL、多通道EDMA控制器、多通道缓冲串口(MCBSP)、I2C接口、HPI接口、EMIF接口等。其中32位高性能外部存储器接口(EMIF)能与SRAM、SDRAM、SBSRAM等同步/异步存储器进行很方便的无缝连接接口,兼容8/16/32位外部存储器总线[7]。本系统上的FLASH、SDRAM及FPGA都挂在DSP的EMIF总线上,方便DSP对其访问和操作:

(1)DSP与FLASH接口:FLASH是一种高密度、非易失性的电可擦写存储器,主要用来存放一些应用程序和其他信息,保证掉电不丢失数据。本系统采用的FLASH芯片为SST公司的SST39LF1601,其容量为2M字节,可在3V~3.6V电压下工作,存取速度为70ns。并把FLASH映射在DSP的CE1空间上,对应的映射地址为0x90000000-0x901FFFFF。其中映射到CE1空间的好处是方便程序的BOOTLOADER,因为DSP上电复位后,DSP内部的EDMA控制器默认会把CE1空间的1KB数据拷贝到地址0处的内部存储器中去,然后运行。所以只要把应用程序烧写到FLASH中,系统就可以脱离计算机正常运行。这里FLASH的另一个作用是保存用于车牌处理算法的一些字符模板信息、特征点信息以及一些用户信息。

(2)DSP与SDRAM接口:SDRAM是同步动态随机存取存储器(Synchronous Dynamic RAM)的缩写,其主要特点为:一是同步访问,读写操作都需要时钟;二是动态存储,芯片需要定时刷新。TMS320C6713的内部存储空间容量无法满足系统程序的需要,而需要外扩高速存储器来提供系统程序的运行空间。此系统中,使用了一片Hydix公司的16位SDRAM HY57V641620,其容量为8M,用于DSP对车牌进行处理时的数据暂存,并把它映射到DSP的CE0空间上,对应的地址为:0x80000000-0x807FFFFF。其工作时钟由DSP提供,本系统设置为100MHz。通过配置DSP的EMIF控制寄存器,可以设置SDRAM的各种参数。

(3)DSP与FPGA的连接:FPGA从视频流中捕获了车牌图像,如何让DSP获取该图像信息进行处理工作,也是本系统设计的一个重点。SBSRAM (Synchronous Burst Static RAM),即同步突发静态存储器,其最大的优点就是支持同步突发访问,访问速度高,而且属于静态RAM,不需要刷新。所以,相对DSP来说,本系统把FPGA配置成SBSRAM来进行访问,会相对简单些,并把其映射到DSP的外部CE3空间。由于本系统设计时,对从FPGA读取的图像数据是以行单位来计算的,每次在FPGA内部存满一行数据,FPGA就发一个中断信号给DSP,让DSP从中把数据通过EMIF口读走,而这里一行的图像数据的信息量为720*8bit,所以系统设计中,地址总线只用到了10位,而数据总线只用到了8位,对应的映射到DSP的存储地址为0xA0000000-0xA00003FF(1K Byte大小),这种设计方法很大程度上方便了DSP对FPGA的访问操作,FPGA与DSP的连接如图4所示。

图4 FPGA与DSP硬件连接示意图

2.2.2 DSP软件编写

DSP作为信号处理芯片,在处理各种信号方面都有着强大的优势。本系统中,大部分图像处理算法(车牌定位、分割、字符识别等)都在其上实现。在搭建好良好的硬件平台后,接下来要做的就是对DSP的编写,这里主要有两块程序的编写:算法的移植和底层驱动的开发。

CCS(Code Composer Studio)是TI公司推出的一套集成开发环境,用它来开发TI的DSP芯片应用程序;其中CCS 中集成的DSP/BIOS[8]是TI公司为C5000系列和C6000系列数字信号处理芯片量身定制的一个嵌入式实时操作系统内核,具有图形化界面、代码快速成型功能以及完备的API函数库等优势,可极大的方便应用系统的开发和在线调试。本系统就是采用CCS2.2中自带的DSP/BIOS操作系统进行程序的开发,使用任务、线程、旗语、邮箱等进行一系列编程,方便的控制程序的实时调度运行。

(1)算法移植:一般算法的编写都会在Matlab上实现,虽然它是一种类C语言,但和标准的C相比还是有着很多的差异,而且Matlab中往往提供了各种信号处理的工具箱,如图像处理、神经网络、小波变换等等。我们只要简单的调用这些函数来,带入几个参数即可以方便的进行各种信号处理。所以,当把这些算法移植到本系统的DSP中时,一些函数还得重新编写,还有编程格式、风格都要有所更改,有些地方为了提高算法的效率,充分利用DSP的资源,还应该把部分代码编写成汇编语言等等。当把整个算法都移植完后,最后封装成一个函数,这样更易于整个算法的维护及调用。然后,当触发条件满足时,用DSP/BIOS中的某个任务来调用这个算法处理函数来完成对车牌图像的识别。

(2)底层驱动的开发:底层驱动的编写采用CCS自带的CSL(Chip Support Library)来进行底层驱动开发,CSL提供一系列应用程序接口(API,Application Programming Interface)用于配置和控制DSP片上外设,从而简化了DSP片上外设的开发工作,大大缩短了开发周期。

2.3 FPGA功能模块

FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。FPGA的使用非常灵活,同一片FPGA通过不同的编程数据可以产生不同的电路功能。FPGA在通信、数据处理、网络、军事和航空航天等众多领域得到了广泛应用。

本系统设计中,FPGA作为图像采集、存储以及传输的核心模块,协调及控制着整个系统的正常运行,起着非常重要的作用。本系统选用了Altera公司性价比较高的Cyclone系列中的EP1C12Q240型号FPGA。该FPGA共有52个存储块,共239616bits。通过QUARTUS II自带的MegaWizard工具可以将每个块配置成不同的存储模式,如单口RAM、简单双口RAM、移位寄存器、ROM和FIFO等,这样有利于本系统在采集图像时暂存图像数据及把FPGA作为SBSRAM供DSP访问的设计。该FPGA有着片上足够多的IO口也为本系统以后扩展留下了空间。

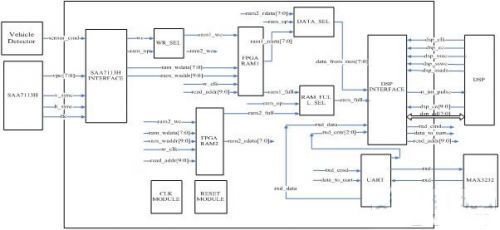

这里与FPGA相连的器件有:SAA7113H、SDRAM、DSP以及MAX3232。由于FPGA纯粹是一个编程器件,其IO脚可以配置成任何我们需要的信号,与任何接口可以相接,所以硬件接口设计上比较简单。难点在于编写各种通信协议和不同的接口进行无缝传输。整个FPGA的程序设计总体框图5所示:方框内的部分为FPGA的各个模块以及它们之间的相互连接。方框以外的部分是FPGA的外围器件。

图5 FPGA的程序设计总体框图

该FPGA系统在整个车牌识别系统中起到图像的采集、缓存和传输的功能。当车辆检测器的感应信号sensor_cmd信号有效时,启动SAA7113H_INTERFACE模块内部的状态机进行图像的采集工作,SAA7113H_INTERFACE模块从SAA7113H的视频流中检测到场开始信号时,开始一帧图像数据的传输。由于视频流为PAL制,所以一帧图像分为奇场和偶场两场图像数据。

系统采用了乒乓结构的设计方法,这种典型的设计方法在"以面积换速率"的FPGA设计方法中经常得到应用。于EP1C12Q240C8内部共有52个存储块,共239616bits,所以在FPGA内部设计一个小存储量的RAM是可行的。系统中设计了两块720*8bits(每行图像数据大小)的空间,这两个存储器的写时钟信号是SAA7113H输出时钟LLC的2倍。SAA7113H INTERFACE模块通过与SAA7113相连的VPO总线,采集标准的YUV4:2:2的Y分量(只采集Y分量目的是得到灰度图像),即其中的亮度信号,一行的图像含有720个亮度信息,亮度信息的位宽为8位。当FPGA_RAM1的图像行满时,发出行满信号ram1_full给DSP_INTERFACE模块,DSP_INTERFACE模块中将该信号转好为中断信号n_int_pulse以通知DSP调用EDMA获取该行的图像。同时进行内部RAM的切换,把下一行数据写入FPGA_RAM2中,保证一边DSP在读取一行图像数据,一边FPGA在写入下一行图像数据给另一个RAM ,以完成一次乒乓操作。

DSP在完成车牌图像的处理后,将车牌图像的识别结果通过EMIF写回到FPGA的DSP_INTERFACE模块内部的寄存器里,并通过UART模块获取这些寄存器的值,通过UART传到PC。

图6所示波形是图5内部框图中的其中一个SAA7113_INTERFACE模块在Modelsim上的仿真波形,从仿真波形中看出,与实际SAA7113输出波形是符合的,达到我们预期的结果。

图6 SAA7113_INTERFACE仿真波形

3、结论

本文所设计的基于DSP和FPGA的嵌入式车牌识别系统,具有速度快、稳定性高、体积小、功耗低等特点,为车牌识别算法提供一个较好的验证平台,如图7所示。经过验证,该车牌识别系统能够实现实时的图像采集、传输、识别。从时间上来考虑,在DSP内部单对一幅车牌图像完成处理(定位、归一化、特征提取与编码)只需不足400ms的时间,速度上来说是非常快的;从识别率上来考虑,只要算法达到一定的要求,经过该车牌识别系统运算后,识别率也是能达到非常高的。总之,该系统在车牌识别方面有着一定的应用价值。

最后,作为一个可以实际使用的车牌识别系统,在以后的系统设计中,还需要增加用于网络通讯的部分、及一些更智能化的功能,如液晶显示、声音提示等等。总之,嵌入式车牌识别系统是当前智能交通应用领域的重要研究课题之一,拥有广阔的应用前景。

- 混合信号微控制器提升车用嵌入式系统(11-08)

- 无线传感器网络在智能交通系统中的应用(02-23)

- 基于OSEK/VDX平台的汽车嵌入式系统开发(06-21)

- 关于公共汽车实时显示及定位系统的研究(05-17)

- 浅谈日本智能交通系统的现状和未来发展情况(04-15)

- 要采用多少车载摄像机解决汽车行驶安全问题?(03-06)