基于KEELOQ的密码系统设计

1 引言

传统编译码芯片如VD5026,VD5027,MCI45026,MCI45027等已经在防盗、安全等系统得到广泛的应用,这些芯片简单易用,但具有很大的缺陷:编码量少而极易重码;密码长度短(一般为8-12位,最多不超过16位),因而数据极易被扫描和破译,不能满足高安全场合的需要。

基于KEELOQ技术的跳码芯片则克服了以上两个缺陷,较好地解决了密码的防盗问题,所谓跳码,就是密码不是固定的,而且不断跳动变化的,是为满足高性能要求而设计的,跳码芯片的使用十分简便,只要在第一次使用前,编译码器进行一次"学习",使编译码器的密码同步,通常一个译码器可以支持多个编码器,再加上其电压使用范围宽,功率消耗极小,因此成为传统编译码器的理想升级换代产品。

2 跳码核心技术--KEELOQ技术

使用KEELOQ技术的编码器每次发出的密码都不同,只有配对的译码器能准确译出收到的密码,使用不配对的编、译码器或重复发送译码器曾收到的密码等均告知无效。即使编码器发送出的码在译码器方没有收到,也不会影响以后的正常使用。这一切归功于芯片内强大的微处理器及KEELOQ独特的同步算法。

跳码芯片的密码虽是一大串几乎随机的乱麻,但实际毫不紊乱,密码包括2部分:

(1)跳码,编译器每次产生的都不一样,产生后就被加密;

(2)在传输过程并不加密,主要包括编码器的系列号,在与译码器的配套使用中作识别信号。

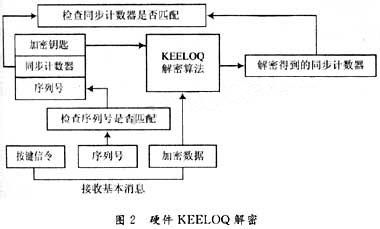

跳码包括功能信息、辨别码以及同步计数器、通过一个加密算法加密后再传送出去。跳码芯片在使用前必须预置序列号、加密钥匙、同步计数器、发送方和接收方一起工作前,接收方必须先通过"学习"来获得并存储发送方的序列号、加密钥匙和当前同步计数器的值。

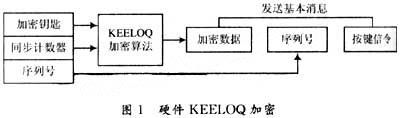

硬件实现KEELOQ技术加密过程如图1所示。

在KEELOQ技术中"学习"功能是一个重要部分,"学习"包括清除原来的存储的信息和学习新的信息,每对跳码型编译码器在使用前都要至少单向"学习"一次,密码在第一次配对使用时是随机产生的乱码。然后把要配对的编码器的密码传进译码器,译码器就会学习和存储这一次的安全代码,从此这一对译码器的密码就按照同一套跳变码算法同步变化,译码器以后每次就能准确译出编码器的密码,同时,这一存入的安全代码被作为无效码参考,再收到同样的密码就会视而不见,因而能有效地防止偷码冒用。

最后,译码器设计了一套容错算法,他不但能预知配对的编码器的下一个密码变化,而且能预知他以后256次的变化码,并都能准确译出,这样,即使发射器被乱按了好多次不为译码器所知,但都能依旧保护默契配合,保持了极好的跳变译码能力和抗截码的功能。

3 应用电路

3.1 HCS301跳码编码器的管脚及其功能

HCS301跳码编码器的引脚排列如图3所示。

引脚1-4:S0-S3,数据输入通道,其中S2,S3在编程状况时可作为时钟输入,引脚5:VSS,电源地;引脚7:LED,指示工作状态及低电压指示,可直接驱动LED,低压时,指示灯将以5次/秒的频率闪烁;引脚8:VDD,电源,工作电压为+3.5-+13.0V。

编码器 HCS301发出的密码长66位,由34位的固定码和32位由KEELOQ算法产生的加密码组成,固定码主要包括28位的系列号(每个编码器独一无二),还含6个状态位,其中2位显示号码是否重复、电源是否低压;另外4位状态位为4位的功能信息(即按键输入组合情况)。32位的加密码中含4位功能信息,以及12位的辨别码(判断译码过程是否有效)和16位同步计数器值。每次按下命令控制键时,译码器的同步计数器的值加1,从冲击的角度看,有一半的位将发生改变,因此相邻的密码将大相径庭。一个相当长的时期内,密码将不会重复,不重复次数可达64K(216),有人统计过,如果每天按10次,那么要经过18年密码才有可能重复。

HCS301还具有独特的电源自动关闭功能,即只有在有编码信号时才进入工作状态,静态功耗极低,降低了电源功耗。通过二极管阵列,HCS301最大可实现15个功能。

3.2 TDH6301跳码译码器的管脚及其功能

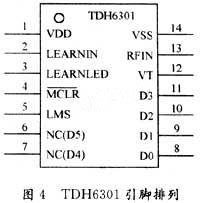

TDH6301跳码译码器的引脚排列如图4所示。

引脚1:VDD,电源,一般接+5V;引脚2:LEARNIN,"学习"键;引脚3,LEARNLED,"学习"指示输出;因该4:MCLR:译码器复位端口;引脚5:LMS,上拉时锁存输出,下拉时暂存输出;引脚6:NC(D5),空引脚;引脚7:NC(D4),空引脚;引脚8- 11,D0-D3,数据输出端;引脚12:VT,接收信号有效输出;引脚13:RFIN,接收信号输入;引脚14:VSS,接地。

TDH6301与编码芯片(HCS300或HCS301)配对使用,可省去了烦琐的编码和配对。他有两种输出方式,当TDH6301的5端悬空时为脉冲型电平输出方式,即无接收信号时,数据输出将保持约500ms;当TDH6301的5端接法如图4所示时为锁存型电平输出方式,即输出电平将保持到有其他输出口接收信号