汽车音响导航系统高速DDR200 PCB的信号完整性设计

CLK→Data→Address/Command

3.5 CLK差分信号的布线方法

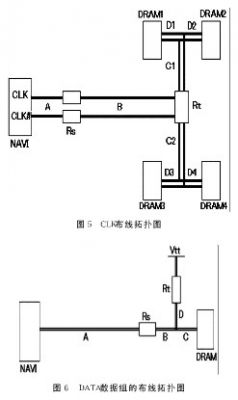

针对DDR200中使用的CLK差分信号,布线拓扑图如图5 .布线注意点如下:

①差分阻抗要实现100Ω。

② 差分对CLK与CLK# 要等长布线,但总长度不要过长。

即CLK( A - B - C 1 - D 1 ) = CLK( A - B -C1-D2)= CLK( A - B - C 2 - D 3 ) = CLK( A - B -C2-D4)3.6 DATA组的布线方法。

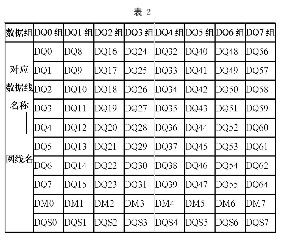

如图6, 标明了DATA组所选的布线拓扑图。布线注意点如下:

① 所有D A T A 信号从N A V I - C P U出发到每个D R A M 的长度都要相等( 即A - B - C段)。

②等长布线的误差可以按同一Bit列及各组Bit间的误差来控制,如表2。

表2

3.7 Address/Command的布线方法

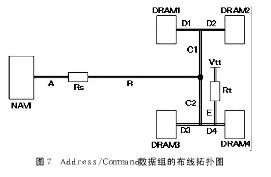

如图7,标明了Address/Command组所选的布线拓扑图。布线注意点如下:

① 总布线长( A - B - C - D ) 等长, 且与CLK间的长度误差控制在一定范围内。

②D段(D1,D2,D3,D4)的布线要等长。

3.8 等长布线的设计方法

为实现DATA组、Address/Command组等网线的等长控制,可以采用曲线(或称矩形线)的布线方法。但若曲线的长度过长或曲线间宽度DM过短,会因为电磁场间的耦合导致信号的传输延迟短于预想时间,过早被传送到接收端,造成信号传输不等时的现象。

3.9 电源与地的布线方法

DDR200所使用的电源有2.5V、3.3V、Vref、Vtt等。布线注意点如下:

①Vref作为输入Buffer用的基准电压,要避免混入其他信号的噪音。布线时要同时注意同层信号间的耦合及相邻上下层间的耦合问题。还要避免跟Vtt(终端电压)的互相干扰。尤其在本例的叠层结构中,要注意与第3层CLK线的层间耦合影响。

②为降低Vtt的走线阻抗,尽可能增加布线宽度,推荐铺电源面。

4 结语

本文在DDR200工作原理的基础上介绍了实现设备高性能的PCB设计方法。如今数字电路已经出现了更高速的DDR2 及DDR3,希望本文的设计思路及高速信号的布线方法能对大家的设计有所帮助。

- 基于龙芯2F的车载和便携设备系统设计(07-23)