用VHDL语言开发的出租车计费系统设计

引言

出租车计价系统较多的是利用单片机进行控制,但较易被私自改装,且故障率相对较高,且不易升级;而FPGA具有高密度、可编程及有强大的软件支持等特点,所以设计的产品具有功能强、可靠性高、易于修改等特点。

本文正是基于FPGA,设计了一种出租车的计费系统,它可以直观地显示出租车行驶的里程和乘客应付的费用。

1 系统功能设计

所设计的计价器的计费标准为:车在行驶3 km以内,只收起步价9.0元;车行驶超过3 km后,按每公里2元计费。行驶路程达到或超过9 km后,车费按每公里3.0元开始计费。车遇红灯或中途暂停时,每3分钟计0.5元。若停止(rst)则车费清零,等待下一次计费的开始。要求能够显示里程数和乘客应付的费用,其中里程数精确到0.01 km,乘客应付的费用精确到0.1元,显示范围为:里程为0~99.99公里,费用为0~999.9元。

2 系统设计方案

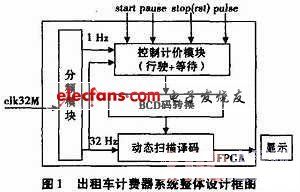

基于FPGA的出租车计费系统的组成如图1所示。由外部输入、FPGA控制部分以及数码显示三部分组成。其中FPGA部分又由分频模块、计价模块、BCD转换模块以及动态译码扫描模块组成;外部输入包括启动按键(start)、暂停按键(pause)、停止按键(stop即rst)以及两个脉冲信号(分别是每20 m一个脉冲的路程脉冲信号pulse和32 MHz的工作脉冲信号clk32M)。显示模块用8个LED数码管分别显示行驶里程和车费,行驶里程显示2位整数和2位小数,车费显示3位整数和1位小数。

3 各模块设计

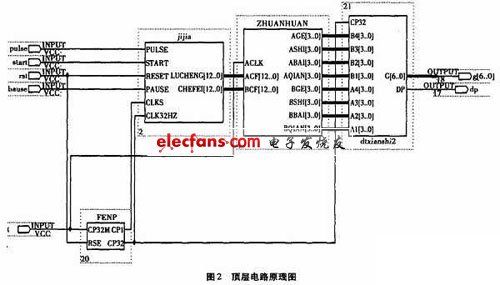

设计FPGA控制部分,包括控制计价模块,BCD转换模块,动态扫描译码模块以及分频模块。采用混合设计的方法,各子部分用VHDL编程,顶层部分用原理图进行设计。

3.1 控制计价模块(jijia)

控制计价模块由里程计费模块、等待计费模块、总价模块组成。

里程计费模块,主要对传感器公里脉冲信号pulse计数(20m一个脉冲),计算出租车本次交易行驶的路程以及里程费用。每数到50个pulse为1 km,总路程由lucheng端输出。在3 km内时,里程车费cf1为9元不变,当超过3 km时,p=1,开始里程费用计数,当计费停止,即start端口置"0"或出租车停止行驶,即rst端口置"0"时,相关数据复位,清零。

等待计费模块,在3 km之后(p=1),每当pause=1时,则开始计时,当秒脉冲数到180个时(即3分钟),此时等待车费cf2加5,表示车费加0.5元。

总价模块是将里程计费和等待计费相加,计算出总费用,从chefei端输出。

3.2 BCD转换模块(zhuanhuan)

该模块将计费模块的车费和路程转换成4位十进制数,便于数码管显示。输入口acf,bcf分别为总路程数的输入口和总费用的输入口,两者都是二进制码进行十进制编码计数,通过该编码器生成BCD码,输出口分别以BCD码表示个,十,百,千位的数据。Aclk是工作脉冲,即32MHz。

3.3 动态扫描模块(dtxianshi)

该模块由动态扫描模块以及译码模块组成。动态扫描模块,该模块利用视觉暂留效应,采用动态扫描电路,将8进制转换后的路程数和车费的4位十进制数显示在数码管上,节约了硬件资源和能源。该模块经过8进制扫描模块将路程和车费轮流显示出来。端口d是选通地址码的输入端口,A1,A2,A3,A4,B1,B2,B3,B4分别是个,十,百,千位的数值输入端口。根据输入的地址码,模块每次只有一位数字向后传输到输出口q,同时输出小数点的显示控制信号(dp),使路程显示为00.00公里,费用显示为000.0元。

译码模块,该模块把0-9的BCD码译成数码管显示码,输入端口q输入扫描模块选出要显示的BCD码,译成数码管的显示码由g[6..0]输出。本设计中数码管是共阴数码管。

3.4 分频模块(fenp)

本设计中输入的系统时钟为32 MHz,进行分频,再对数码管的地址进行扫描。输入端口rse为出租车停运信号输入端口,当出租车停止时,该模块停止工作,清零。当出租车行驶时对输入的32 MHz脉冲信号进行分频,分别从输出端口cp1得到秒脉冲,cp32得到32 Hz工作脉冲。

3.5 整体电路

将各个模块按照输入输出关系连接,顶层电路原理图如图2所示。g[6…0]为七段显示码输出,通过动态扫描依次控制8个数码管的显示,dp为小数点位。

4 系统仿真验证

用MAX+plusⅡ软件对各个子模块及顶层原理图进行了时序仿真,仿真波形如图3所示。

控制计价模块仿真图如图3所示。由图3(a)可得,当reset=1,start=1,且pause=0时,表示出租车处于行驶状态,此时路程开始递增,当不超过3 km时,车费为5A即90,起步价9.0元。由图3(b)可得,当超过3 km后,车费每行驶1 km加20(即2元)。由图3(c)可得,当reset= 1,start=1,且pause=1时,出租车处于等待状态,此时路程不再递增,而时间递增,当时间达到3分钟时,车费加5(即0.5元)。

顶层电路的仿真图如图4所示。从图中可以看出,随着输入的变化,从g[6…0]输出了共阴的数码管显示编码,dp也在对应的数码管处,输出高电平点亮小数点。本设计的软件仿真结果正确,达到预期目标。

- FPGA技术在汽车电子中的应用(11-26)

- 汽车尾灯VHDL设计(04-03)

- 移动智能车辆稽查系统的设计与实现(09-29)

- 先进的配电系统设计工具为向电动汽车的过渡铺平道路(07-20)

- 高性能汽车和FPGA?——共同点比您想象得多(03-27)