CAN标准中的时钟容差修正建议

时间:01-08

来源:

点击:

(2×△f)×46×NBT≤SJW (4)

仍以第一部分中例子的数据,NBT=8,SJW=1,可得△f≤0.001 35,又小了一些。如果在某系统中有NBT=25,SJW=1,可得△f≤0.00043。这是相当小的值。

根据上述分析,最坏的情况是(4)式。对于CAN2.0 A,对应可以导出最坏情况为:

(2×△f)×21×NBT≤SJW (5)

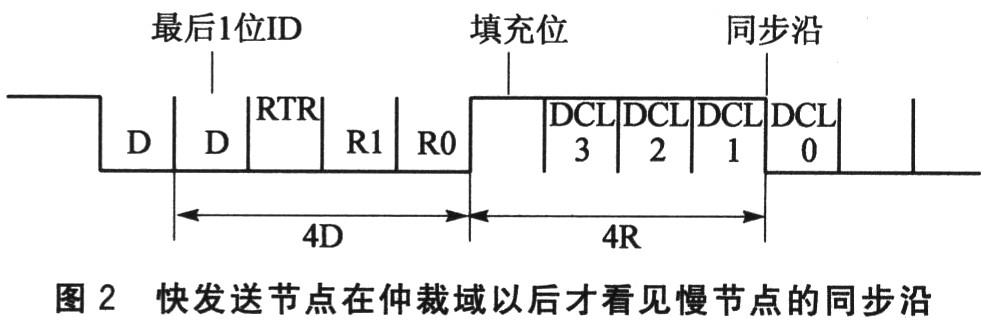

如果传输时间比较短,慢节点已按快节点延迟Pr/2后进行了同步,那么在慢节点最后胜出的那一位,快节点将见到e=Pr的来自慢节点的同步沿。为能保证同步,至少应有:

Pr≤SJW (6)

如果(6)式满足,就可以发生同步。例如在传输延迟占位时间份额小的系统,用原ISO11898-1的算式。使用中,读取ACK位时,最坏的同步沿将相隔 11位(CRC分界符不在填充位规则内),(1)式还应该修改。如不满足(6)式,例如高速系统,就应考虑(4)或(5)式。ISO11898-1应添加上述内容。一般地说,(4)、(5)式比(1)、(2)式要求严格,如需要简化,用它们就足够了。例如对于CAN2.0A,用前面例子的数据,NBT=8,SJW=1,由(5)式可得△f≤0.002 97,也优于原来的0.004 90。

3 ISO 16845:2004应添加的条款

ISO16845关于发送器时间同步相关功能的一致性测试条款共9项(8.7.1~8.7.9),其中用于有相位差的重同步仅2项:8.7.4款,当 e<0且|e|≤SJW时的同步;8.7.5款,当P<0且e>SJW时的同步。由第2部分的分析可知,发送器在仲裁中退出的最后一位是需要进行同步的,此时它还是发送器状态。只有同步以后,才能正确采样,决定是否退出并保证退出以后能正确跟踪胜出的发送器。因此,需要添加 e>O,且| e |≤SJW,以及e>0,且| e |>SJW时的测试条款。这些条款可以参考接收器的相应条款(7.7.3和7.7.4)。

ISO 16845中的低层测试设备LT是专用设备,它与被测的CAN(称为被测试的实现IUT)的Tx、Rx相连,LT产生必要的输入条件到Rx,然后从Tx测取IUT的反应是否合格。非测试输入时LT不应影响IUT。以e>O且|e|>SJW时的测试为例,安排IUT发1帧在ID域带填充位为显位的帧。当发到第5个隐位时,LT延迟e将Rx变为显位,然后在延迟后的新采样点(原P1+SJW)处为Rx建1个隐位值,此时IUT的输出Tx将在LT提供的R/D跳变沿后一位按同步规则提供显位,如图3所示。上述测试设计基于如下原理:如果IUT动作正常,它将同步于LT提供的R/D跳变沿,并采到LT 提供的隐位,这时发出它的下一个填充位,填充位的R/D跳变沿已被IUT先前的同步所移动。如果同步不正常,或者跳转的量不对,IUT将采到显位,它会仲裁失败而退出,不会再发送。测试的P的范围是(SJW+1)~(NBT-P2-1)。这个设计不同于标准的7.7.4款。笔者认为7.7.4款的方法是不能达到目的的,该问题的详细讨论超出了本文的范围,不再赘述。

4 小 结

CAN的一般技术资料均提到,高速时的可靠性要比低速时的差,应用中能用低速就用低速。从上述位同步时钟容差的分析可知,高速时时钟容差小,所以一旦时钟有问题就会影响同步与采样。CAN标准ISO11898-1:2003仅考虑了部分场合的要求,对发送器仲裁阶段未能同步的情况未作考虑,从而给出的容差结果偏宽,设计者有可能依此选用不合适的振荡源,造成电子控制器(ECU)可靠性不够。例如,现在已经有一些精度接近0.3%~2%的可修正的RC或 CMOS振荡器,它们价格低,接近原CAN标准设计的容差,有可能被不适当地选用。所以对标准加以补充是十分必要的。随着CAN应用的扩展,提高CAN工作频率的努力也在继续。一方面,有些应用可缩短传送距离以使传输时间缩短,例如机器人、武器等;另一方面,CAN的性价比高,对这类应用有吸引力,在传输时间接近临界情况的场合,更要注意时钟容差的问题。

从另一个角度考虑解决问题的可能性是:将仲裁域中及仲裁后的第1个同步沿发送器与接收器的同步均设为硬同步。这种做法可以改善同步以后的采样,但对同步以前的采样没有改善,它们仍然要求较高精度的时钟来保证采样点在缓冲段P1、P2之内。而且,过多的硬同步增加了对干扰进行不必要同步的机会,反而不是好事。因此这种方案是无价值的。

从分析可知,当重同步跳转宽度SJW可选得较大时,容许的时钟偏差就较大。不受限制的SJW相当于随时执行硬同步,小于P1、P2的SJW就使采样点的变动较小。当总线上由于干扰出现假的R/D跳变沿,就会引起错误的重同步,小的SJW有助于降低读错概率。因此,兼顾减少出错率与降低时钟容错限的要求,关键是设计一种性价比好的滤除干扰的办法。 (编辑:chiying)