利用高速ADC设计用于汽车的LIDAR系统

时间:02-23

来源:半导体应用

点击:

多个ADC的同步实现

多个ADC交替工作来增加采样速率,这个采样速率是单个器件目前尚不能达到的。增加采样速率的好处是可以得到更精细的脉冲形状和更高的时序精度。本文谈到的一个ADC固有的挑战是ADC输出数据流的同步。系统开发者必须准确地知道ADC输出的哪个字(word)对应于系统前端采样的脉冲。

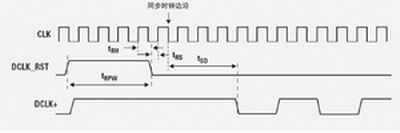

为简化这种时间交替处理,采用ADC08Dxxx系列芯片能够准确地复位其采样时钟输入与数据输出时钟(DCLK)输出之间的关系,这种关系是由用户提供的DCLK_RST脉冲决定的。这样可以允许一个系统中的多个ADC的DCLK(和数据)输出转换可以与它们用来采样的共享CLK输入发生在同一时间点上。

图3 DDR模式下DCLK的复位时序。 同步时钟边沿

信号在FR04 PCB上的传输速度为20cm/ns(即每50ps1cm),如果ADC相互并不是很靠近的话,图3中的设计时间是难以实现的。在这情况下,建议短时间(小于50ns)停止时钟,这样,在DCLK_Res置位期间维持交流耦合。推荐输入时钟采用交流耦合。交流耦合电容的时间常数是50 Kø(内部偏置电阻)×4.7nF(外部交流耦合电容) = 235 μs。因此,不必考虑时钟停止50ns以内将对交流耦合电容起到很强的去偏置作用。

此外,也可在时钟接收器中使用占空比稳定器(缺省配置),其校正时间常数很短(100ns~500ns),并且限制反转。同样因为这个原因,一旦时钟运行超过3ms就可以在耦合电容上建立正确的电压,时钟停止的时间不能超过50ns。在时钟停止的时间内,可以对DCLK_Res异步复位。

结语

ADC08Dxxx系列ADC器件结合了低功耗和卓越的动态特性,在保持7.0有效位数(ENOB)的条件下,能对模拟信号进行高达3GSPS采样,为高精度LIDAR系统提供了很好的解决方案。以ADC08D1000为例,在1GSPS采样速率下实现7.5ENOB,其输入带宽为1.7GHz,在很多应用中可以直接实现RF变换,不需要高成本且复杂的下变频电路模块。多ADC同步等集成的功能大大简化了时间交替处理的板级实现过程。在双沿采样(DES)模式下,通过交替使用两个1.5GSPS的ADC,可以实现6GSPS的采样速率,这样能提供+/- 2.5 cm/m的分辨率。

系统设计工程师还可以采用WaveVision 4.0 ADC评估板进行系统开发,该评估板提供了连接PC的USB接口和支持软件。利用WaveVision 4.0评估板可通过PC捕捉来自ADC的各种波形数据,并以图形形式显示出来,方便进行波形检查,也可用有关数据进行快速傅立叶变换(FFT)计算,以便衡量ADC转换器的动态性能,显示信噪比、总谐波失真和无杂散动态范围(SFDR)以及快速傅立叶变换得到的光谱图。这些对于需要进行评估及调试的设计师来说非常重要,采用这些软硬件工具,设计师甚至可以分析电路板噪声的振幅及频率。

- 采用MPC5200实现高速视频探测的车内应用(02-22)

- 指纹产品在汽车领域里的应用(02-22)

- 直接式胎压监测系统的设计(02-22)

- 汽车电动助力转向系统的技术分析(02-19)

- 基于铁电存储器的高速和高保真的汽车事故实时数据记录仪(03-23)

- IIHS公布81种乘用车座席及头枕安全性评价结果(03-10)