剖析半导体工艺制程节点,被终结的摩尔定律是狭义的

翻番。因此,出现了90纳米、65纳米、45纳米、32纳米--每一代制程节点都能在给定面积上,容纳比前一代多一倍的晶体管。

但是最近,也许是因为进一步的制程升级越来越难,一些公司背离了摩尔定律的法则。即使晶体管密度增加很少,或者根本没有增加,但他们仍继续推进采用新一代制程节点命名。结果导致制程节点名称根本无法正确体现这个制程位于摩尔定律曲线的哪个位置。

行业亟需一种标准化的晶体管密度指标,以便各个厂商公平竞争。客户应能够随时比较芯片制造商不同制程的产品,以及不同芯片制造商的同代产品。挑战在于,半导体制程以及各种设计日益复杂。

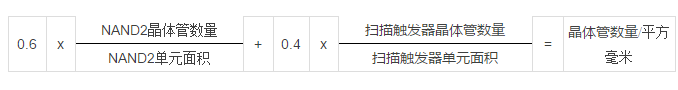

一种简单的指标就是用栅极距(栅极宽度再加上晶体管栅极之间的间距)乘以最小金属距(互连线宽度加上线间距),但是这并不包含逻辑单元设计,而逻辑单元设计才会影响真正的晶体管密度。另一种指标--栅极距乘以逻辑单元高度--是纠正上述缺陷而朝着正确方向迈出的一步。但是这两种指标,都没有充分考虑到一些二阶设计规则。它们都不能真正衡量实际实现的晶体管密度,因为它们都没有试图说明设计库中不同类型的逻辑单元。此外,这些指标量化了比较上一代的相对密度,而真正需要的是给定面积(每平方毫米)内的晶体管绝对数量。在另一种极端条件下,用一个芯片的晶体管总数除以面积毫无意义,因为大量设计决策都会对它产生影响--例如缓存大小和性能目标等因素,都会导致这个值发生巨大变化。是时候让我们重新启用曾经流行但一度"失宠"的一个指标了,它基于标准逻辑单元的晶体管密度,并包含决定典型设计的权重因素。尽管任何设计库中都有各种标准单元,但是我们可以拿出一个普及的、非常简单的单元--2输入 NAND单元(4个晶体管),以及一个更为复杂、但也非常常见的单元:扫描触发器(SFF)。这能够推导出之前接受的晶体管密度测量公式。

(权重0.6和0.4反映一个典型设计中非常小和非常大的单元的比率)

每个芯片制造商在提到制程节点时,都应披露用这个简单公式所测算出的MTr/mm2 (每平方毫米晶体管数量(单位:百万))单位中逻辑晶体管密度。逆向工程公司可随时验证这个数据。

还缺失一个重要的指标:SRAM单元尺寸。由于不同的芯片中有各种SRAM到逻辑比率,最好在NAND+SFF密度指标旁边,分别标注SRAM单元尺寸。

通过这些指标,我们可以拨开迷雾,厘清制程节点命名的混乱状况,从而专心致志推动摩尔定律向前发展。

- 摩尔定律将死带来全球产业链重新洗牌机会(03-08)

- 晶体管进入3-D时代!(05-06)

- 美物理学家称摩尔定律将在10年内崩溃(05-04)

- 晶圆技术将摩尔定律延伸至20纳米(06-18)

- 奈米碳管:半导体持续摩尔定律步伐前进动力?(11-05)

- 摩尔定律快不行?MIT:莱特定律更准(03-12)