ADI最新推出的SHARC系列32位浮点数字信号处理器

在对专用系统实现浮点处理时,以往需预留电路板空间以容纳多处理器和片外存储器,而今,设计人员可以更轻松、更经济地实现浮点处理,将单芯片设计的灵活性和高端处理能力带到大批量市场应用中。利用ADI最新推出的SHARC系列32位浮点数字信号处理器(DSP),现在设计者可比以往任何时候都更好地利用浮点处理精度,而不必牺牲系统功率预算、电路板空间或元件成本。

SHARC 2148x和SHARC 2147x系列处理器简介

内部集成高达5 Mb内存并实现性能和价格最佳平衡的SHARC 2148x 高性能系列和SHARC 2147x低功耗系列处理器将单芯片浮点高精度信号处理扩展到更广泛地应用系统中,并可在便携设备中实现高端系统功能。通过SHARC 2148x及SHARC 2147x处理器,设计师可以利用端到端 SHARC 系列的代码兼容性及鲁棒的ADI开发工具套件,通过业界性能最佳的32位浮点DSP平台来实现更高水平的开发效率和设计创新。

SHARC 2148x系列高性能处理器

SHARC 2148x系列处理器比同类竞争的32位浮点DSP产品在性能上提高了33%(400MHz),片上存储器增大250%(5Mb),彰显了SHARC 2148x系列作为高清晰度(HD)音频和家庭影院应用以及高级工业应用的处理器首选所具备的特质,因为这些应用的需求是:单芯片、具备浮点精度且价格便宜。

SHARC 2147x系列 低功耗高精度处理器

便携设备应用如高级驾驶员辅助系统(ADAS)需要浮点处理精度并且具备低功耗和适应极恶劣的环境条件,而新款12x12mm SHARC 2147x系列处理器功耗仅为363mW(典型值),比同类竞争处理器降低达20%,并提供最高266MHz的性能,片上存储器空间高达5Mb,相比其它任何同类浮点DSP产品,每平方毫米可提供更高的性能和存储器集成度。

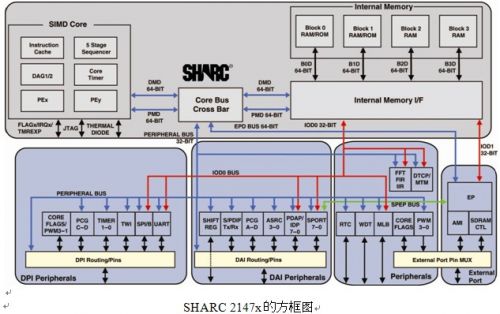

处理器架构和特性概览

高级SHARC系列处理器特性

新型SHARC 2148x 和SHARC 2147x处理器具备专用的硬件加速器和独立的计算单元以及DMA存储映射,实现了后台执行FFT/FIT/IIR信号处理工作的能力,可减轻核心处理负担。 存储器的使用率是通过变量指令集架构(VISA)支持实现优化的,这样可以通过缩减指令操作码大小为应用代码释放多达30%的存储空间。

SHARC 2148x和SHARC 2147x处理器集成了专为简化硬件设计、使设计风险最低并最终缩短上市时间而设计的专用外围设备,这些功能块统称为数字应用接口(DAI),它们可以彼此连接或通过软件可编程的信号路由单元(SRU) 连接到外部引脚。SRU是一个创新的架构功能,可以在DAI模块之间灵活地实现完整的路由。通过SRU连接的外设包括但不限于串行接口、SPI端口、S / PDIF Tx / Rx和8通道异步采样率转换器模块。

应用亮点

为高清音频和家庭影院应用提供同类最佳的价格/性能

集成以音频为中心的外设和专用片上解码器来实现高性能音频产品设计,SHARC2148x处理器使设计师能以不断减小的外形尺寸开发出功能丰富、价格具有竞争力的高清音频和家庭影院系统。SHARC级别的算法处理因实现优美的音质和高级数字音效而享誉专业音频市场,现在也可用于要求低成本、单芯片电路板实现的消费类AVR系统。

针对便携式医疗设备的低功耗、精密处理

对于诊所、救护车和其它非医院环境下医疗专业人员所配备的便携式医疗设备,低功耗SHARC2147x处理器也是理想选择。基于SHARC2147x的医疗设备可确保高精密的信号处理,可得到精确的病人数据,方便医疗专业人员快速制定治疗方案。

适合基于雷达的汽车电子应用/ADAS的浮点精度

SHARC2147x处理器提供的计算精度有利于提升基于雷达的ADAS性能,包括自适应巡航控制、盲点检测及十字路口交通警告,为苛刻的安全应用实现最佳的目标分辨、多目标跟踪及实时系统响应。 具备低功耗属性并且能适应105℃环境工作温度,SHARC2147x处理器满足了汽车环境需求并且具有价格竞争力,可帮助降低ADAS 选项打包价格并加速消费者的接受和采用。

超高效率的电机控制

SHARC2148x处理器为设计师提供他们所需的性能、处理精度及外设,以开发具有成本效益的新一代电机驱动和工业控制系统。 设计师可以利用可视化开发软件来实现高级算法,以获得动态系统控制及更高的能效,同时减少设计复杂度并加快上市时间。

ADI 的SHARC ®浮点数字信号处理器

ADI公司32位浮点SHARC数字信号处理器采用超级哈佛架构,可很好地在优异的内核和存储器性能与突出的I / O吞吐能力之间取得平衡。超级哈佛架构通过加入一个I/O处理器以及与之相关的专用总线扩展了最初将程序和数据存储器总线分开的理念。除了满足计算最密集、实时信号处理应用的要求之外,SHARC处理器还集成了大容量的存储器阵列和专用外设,可简化产品开发和缩短

- ADI 样片最快三天送至客户(07-19)

- 中国IC产业急速转型,ADI加大免费样片投入应对研发需求(12-27)

- ADI推出业界最低功耗模拟微控制器(06-08)

- ADI推出适合汽车视频的高速视频放大器(06-15)

- ADI打造绿色MEMS(06-27)

- ADI推出开关稳压器简化负载点设计(07-19)