赛普拉斯新型West Bridge?嵌入式应用控制器 具备市场上最快数据通讯能力

时间:11-10

来源:与非网

点击:

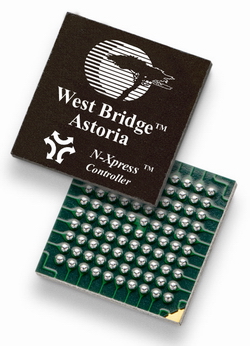

赛普拉斯半导体公司(纽约股票交易所代码:CY)近日推出了一款具备多层单元(MLC)NAND闪存支持能力的新型West Bridge™外设控制器,可为设计者采用成本最低、密度最高的闪存存储器提供支持。这款West Bridge Astoria™控制器最高支持16个MLC NAND闪存设备,而MLC NAND闪存与相同存储密度的单层单元(SLC)NAND闪存相比,其成本降低了三倍。

新款控制器提供了与West Bridge Antioch™控制器相同的领先业界的高速USB数据传输性能。在最近一项对顶级多媒体手机的数据传输性能进行的对比中,Semiconductor Insights发现,使用Antioch控制器的手机,其文件传输速率要比其它接受测试的高速USB手机的文件传输速率快2倍以上。对比详情请访问www.eetimes.com/showArticle.jhtml?articleID=203101718。Astoria控制器通过一个可配置型多媒体存储器接口以及灵活的处理器接口增加了此项性能,方便了与各种嵌入式处理器和大容量存储设备的连接。这些新特色让Astoria控制器能够连接任何嵌入式处理器或DSP,为各类新型应用带来MLC NAND支持能力,其中包括便携媒体播放器(PMP)、无线网卡、收发器(dongles)、便携导航设备(PND)、数码相机、POS终端以及其它许多应用。

赛普拉斯半导体公司具备多层单元NAND闪存支持能力的新型West Bridge™外设控制器 通过将嵌入式处理器完全从USB和存储器管理负荷中解放出来,West Bridge Astoria外设控制器节约了至关重要的处理器资源,并最大程度地提高了数据传输性能。这款控制器产品标志着赛普拉斯的快速交叉编码N-Xpress™多层单元NAND闪存控制技术的初展身手,这项技术具备了静态磨损均衡控制、坏区块管理以及4位ECC(纠错编码)特色,可支持最多16个SLC/MLC NAND设备。通过对存储器端口的配置,设计者可以最多选择2个SDIO设备,例如蓝牙、WiFi、GPS和SD卡,从而让Astoria成为数据存储卡和收发器类应用的理想控制器。Astoria还支持其它类型的存储器,这些存储器包括了高容量安全数字卡(SDHC)v. 2.0、多媒体存储卡++ (MMC+) v. 4.2、符合CE-ATA标准的HDD,以及各种类型的受控型NAND。它可通过灵活的处理器接口与绝大多数嵌入式处理器连接,为Antioch的伪CRAM接口添加了更多的接口,如异步SRAM、ADMUX(地址数据复用)、SPI(串行外设接口)以及NAND接口。赛普拉斯West Bridge业务部副总裁Alakesh Chetia表示:"赛普拉斯的West Bridge Antioch控制器产品之前已经广范获得成功,在手机与PC机之间提供了最快的数据传输性能,让用户能够在不到1分钟的时间内下载1GB的存储内容。我们新的Astoria控制器能够为许多类型的处理器和存储器提供同样优秀的数据传输性能,而且采用了灵活的处理器接口、可配置存储器接口,此外还采用了我们的N-Xpress MLC NAND控制器技术,将West Bridge的概念扩展到了更多类型的嵌入式应用之中。" 总部位于加利福尼亚州El Segundo的市场研究公司iSuppli Corp的内存IC和存储系统部门主管兼首席分析师金南衡指出:"MLC NAND闪存正越来越多得到人们的欢迎,这是因为它比SLC NAND具有更高的密度,以及不断拉开的成本差距。随着所有嵌入式应用中对更高密度存储器需求的稳定增长,必然要求提供对于MLC NAND的系统支持。" West Bridge Astoria控制器的特色包含最多27个可编程通用输入输出(GPIO)引脚和16个USB端点。这款产品采用了小巧的100-ball VFBGA封装,尺寸仅为6 mm x 6 mm,引脚间距0.5-mm。此外,Astoria还支持19.2 MHz和26 MHz等手机频率作为时钟输入,从而无需再多配置1个晶振芯片。 West Bridge系列产品简介 新型West Bridge外设控制器系列产品中的各款器件产品可以作为嵌入式中央处理单元(CPU)的协处理芯片发挥作用,将CPU从数据密集型运算中解放出来。同样地,PC机架构中已经引入了南桥和北桥架构,以便让主CPU能够独立于快速变化的存储器和外设接口而变化。嵌入式系统也正朝着类似的架构演进着,而West Bridge器件起到了管理各个接口以及减轻CPU对具体外设间数据传输的管理负担的作用。 West Bridge系列产品以赛普拉斯公司Simultaneous Link to Independent Multimedia™ (SLIM™)架构为基础,能够管理各外设、存储器以及处理器之间的多个专用路径,以实现最大的数据吞吐量。除了提供了一种不需要主处理器支持的通向接口的路径外,SLIM架构允许从一个接口向另一个接口进行直接而独立的数据传输,减轻主CPU的负荷,将CPU资源解放出来,以实现更高的系统性能。 |

赛普拉斯半导体公司 蓝牙 WiFi GPS PMP 相关文章:

- Vishay推出超小型SMD石英晶振XT23和XT35(07-13)

- 不需要电池的无线通信技术(08-03)

- 观点:NFC技术将是蓝牙在汽车领域的补充性技术(08-16)

- 无线技术在LED照明中的应用发展(06-14)

- 蓝牙成为苹果无线技术的核心(06-19)

- 苹果产品系列全面进入蓝牙4.0生态系统(09-25)