IBM/三星/格罗方德共同研发5nm芯片,商业化还要多久?

相较于市场上的10纳米技术,5纳米制程可在相同的耗电下提高40%的效能,或是在相同效能下减少75%的耗电,对于节能或仰赖更高运算的人工智能、VR、云端应用大有帮助。

IBM于周一(6/5)宣布,已与三星、GlobalFoundries及其他设备供货商共同开发出可打造5纳米芯片的制程,并准备在本周于日本京都举行的2017 Symposia on VLSI Technology and Circuits研讨会中公布细节。

相较于7纳米芯片可存放200亿个晶体管,5纳米技术则可在指甲大小的芯片上存放300亿个晶体管。 若相比于市场上的10纳米技术,5纳米技术在固定的用电量上可提高40%的效能,或是在同样的效能上可减少75%的电力损耗,不论是对未来的人工智能系统、虚拟现实或是行动装置的应用都将大有帮助。

5纳米芯片主要仰赖了堆栈的纳米片(nanosheet)与超紫外线(Extreme Ultraviolet,EUV)蚀刻技术。

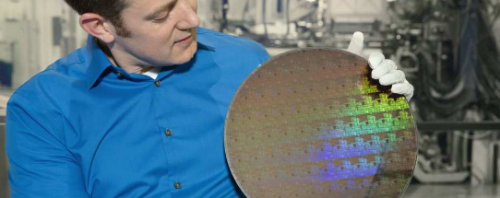

5纳米下的硅纳米片晶体管:(来源:IBM)

有别于现在市场上主流的鳍式场效晶体管(Fin Field Effect Transistor,FinFET),纳米片是由横向的gate-all-around (GAA)晶体管所组成。

IBM表示,他们研究纳米片技术的时间已超过10年,这是业界首次有人能够示范让堆栈纳米片装置的电性优于FinFET架构在设计与制造上的可行性,而纳米片晶体管架构也将取代FinFET主导7纳米芯片之后的制程发展。

另一方面,用于生产7纳米芯片的超紫外线蚀刻技术也被应用在基于纳米片的5纳米芯片上,该技术可在单一生产制程或芯片设计上持续调整纳米片的宽度,能够微调特定电路的效能与电力损耗,而这是受限于鳍高度的FinFET架构制程无法达到的。

有鉴于7纳米芯片要到明年才会商业化,5纳米芯片真正落实在商业产品上的时程可能还要好些年。

- 全球IC代工版图生变 代工版图的基因分析(03-05)

- IBM芯片业务:GlobalFoundries愿买 美国愿卖么?(08-03)

- 采用铜锌锡研制光伏电池 IBM打破世界纪录(08-22)

- 自毁芯片可避免战场情资外泄(02-07)

- 传IBM欲出售芯片业务 将为20年来最大战略调整(02-10)

- Semico研究认为2010年全球IC业将强劲增长(09-26)