存储器还能当处理器使?科学家用了啥方法

新加坡南洋理工大学、德国亚琛工业大学和尤利希研究中心的科学家团队找到了一种方法让记忆芯片执行传统上由处理器完成的计算任务。这意味着存储芯片能在存储数据的同一位置处理数据,将有助于创造出更小更快更薄的移动设备和计算机,通过减少处理器而节省空间。

新的计算电路使用了SanDisk和松下等公司研发的电阻式随机存取内存(ReRAM)芯片,研究显示ReRAM芯片不仅可以储存数据,还可以处理数据。研究报告发表在《Scientific Reports》期刊上。

什么是ReRAM?

ReRAM(可变电阻式存储器),将DRAM的读写速度与SSD的非易失性结合于一身。换句话说,关闭电源后存储器仍能记住数据。如果ReRAM有足够大的空间,一台配备ReRAM的PC将不需要载入时间。

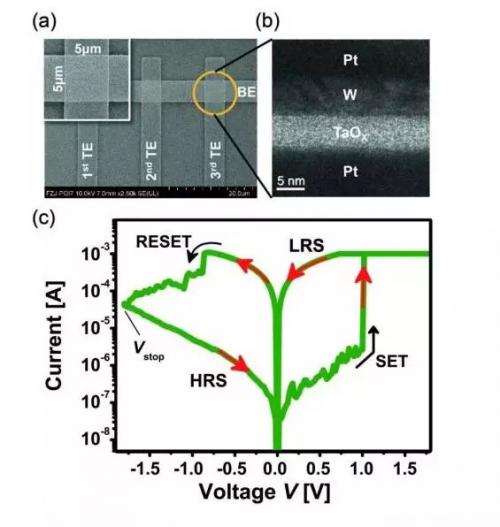

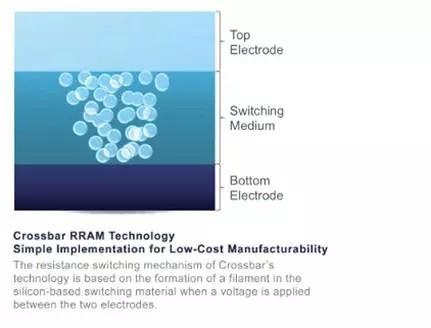

ReRAM一直被认为是未来闪存的替代方案,能在单块芯片上存储1T数据,存取速率比闪存快20倍。典型的ReRAM由两个金属电极夹一个薄介电层组成,介电层作为离子传输和存储介质。选用材料的不同会对实际作用机制带来较大差别,但本质都是经由外部刺激(如电压)引起存储介质离子运动和局部结构变化,进而造成电阻变化,并利用这种电阻差异来存储数据。

一个典型的ReRAM单元具有一个转换材料,它具有不同的电阻特性,并且被夹在两个金属电极之间。ReRAM的转换效应是基于在电场或者高温的影响下产生的离子运动以及转换材料存储离子分布的能力而实现的,从而引发设备电阻的可度量变化。

有很多不同的方法来实现ReRAM,它们采用不同的转换材料和内存单元组织结构。不同的材料所具有的不同变量可以导致显著的性能差异。ReRAM技术最常见的挑战在于热敏度、与标准CMOS技术和制造工艺的整合、以及每一个ReRAM单元的选择机制。

ReRAM内存的性能和比特/尺寸密度取决于内存单元的内联方式。嵌入式低延滞、高速内存可以通过用一个晶体管对每一个内存单元进行单独控制来实现。在1T1R(每1个ReRAM单元有一个晶体管)的阵列组织结构中,内存的总体积由晶体管的体积所决定。高密度存储级内存要求一个密度高得多的内存阵列组织结构来实现成本效益,这就要求能够用一个单一的晶体管来连接成千上万的内存单元。这种1TnR组织结构只有当ReRAM单元具有某种内建的选择机制,可以单独地、或者不指定地选择ReRAM单元时才有可能实现。

ReRam通过改变cell的电阻来存储数据。目前有各种各样ReRam技术正在开发之中,包括相变内存(PCM)和惠普Memristor技术。

随着更多细节的透露,我们期待这个行业将形成良性竞争态势。

ReRAM的优点

虽然有不同的规格,但是所有ReRAM都具有当前NAND闪存拥有的主要优点:

速度 ReRAM写速度更快--以纳秒为单位而不是毫秒--使它更好适应于高性能应用。

耐用性 最常见的MLC闪存只能处理10000次写操作,而ReRAM却可以处理数百万个。

功率 研究人员已经证明微安培写入功率并期望很快将进一步降低到纳安范围,这使得ReRAM比NAND闪存能效更高。

在可预见的未来,NAND闪存将保留在成本和密度上的优势,这意味着它仍将在未来几十年存活下去。那么ReRAM在存储层中的定位是?

数据完整性 丢失一个快照是没有什么大不了的。丢失你的支票帐户存款就不一样了。关键任务应用更喜欢ReRAM,而且关键是买得起。

性能 固态盘这种高速存储介质消除了复杂性并提高了性能。

移动性 网络宽带和内存容量之间进行着一场永无止境的拉锯战,在这种情况下,消费者可能会喜欢上他们移动设备的大容量存储。如果是这样, ReRAM节能的优点将在高端产品有所体现。

东芝凭借其类似于今天1.5万转硬盘的固态硬盘,开始涉足这些高端市场。这可能不是一个巨大的市场,但是其高利润率还是值得一试的。

其他厂商,包括松下、美光和三星,也正在致力于ReRAM的研发。另外一个有趣的问题是:在系统中ReRAM多大程度上能替代高速DRAM?

三进制的ReRAM提供处理能力

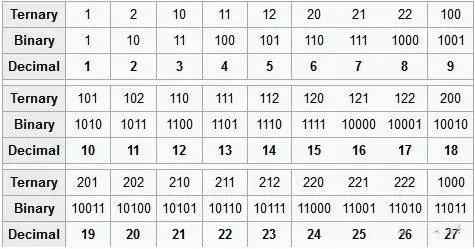

目前,市场上所有的计算机处理器,都使用了二进制系统,即数据由两种状态组成,0或者1,例如字母B,在计算机内就存储为「01000010」的形式。

数字1到27,三进制(第一行)、二进制(第二行)、十进制(第三行)数字对照表。

然而,ReRAM 电路所表示的数据状态,并不是0和1两种,它可以存储和处理数码有:0、1、2,即「三进制数字系统」,从而可以存储更多的数据状态。

原因就是,ReRAM使用不同的电阻来存储信息,从原理上来说,可以突破现有二进制系统的限制,显著提升计算任务的处理速度。

来自南洋理工大学的计算科学和工程系助理教授Chattopadhyay 是该存储器三进制系统的主要设计者

- DRAM合约价酝酿反弹 暂无崩盘之忧(02-18)

- 科学家发明新技术 可让手机充一次电使用数月(03-15)

- 存储器模块业淘汰赛再起 台美联手击退日系阵营(04-11)

- 存储器思谋发展(05-23)

- DRAM厂抢进移动式存储器 下半年价格添隐忧(06-15)

- DRAM厂抢进行动式存储器(06-15)