富士通内部工艺技术资料,11步造出啥芯片

在半导体的生产工厂,在晶元上通过极其细微的加工进行制造。在一枚晶片上一共要制造出成千上万个这样的十几毫米大小的半导体器件(芯片)。这道制造工序叫做晶元工艺,这道工艺的流程则被称为Process Flow(工艺流程)。 今天咱们就简要介绍下半导体IC的Process Flow。

FEOL(Front End of Line :基板工序、半导体晶元制造工序的前半部分)在硅基板上制造出晶体管等部件。

BEOL(Back End of Line:布线工序、半导体晶元制造工序的后半部分)将在FEOL制造的各部件与金属材料连接布线,以形成电路。

1、元件隔离

晶体管是在硅晶片的表面附近形成晶。 为保证每个晶体管的独立运行,需要阻止与之相邻的晶体管的干扰。因此,晶体管的形成区域是相互隔离的。

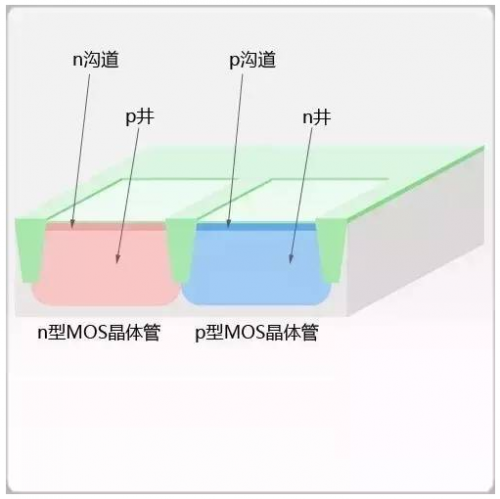

2、井道形成

在一个芯片中,分别制作出n型MOS晶体管与p型MOS晶体管。 在各自的晶体管制作区域,以适当的浓度的注入各个晶体管所需的杂质(n型MOS:p井,n沟道;p型MOS: n井,p沟道)。另外,可通过追加掺入不同的杂质及不同浓度的剂量來分别制作不同电压/特征的晶体管。

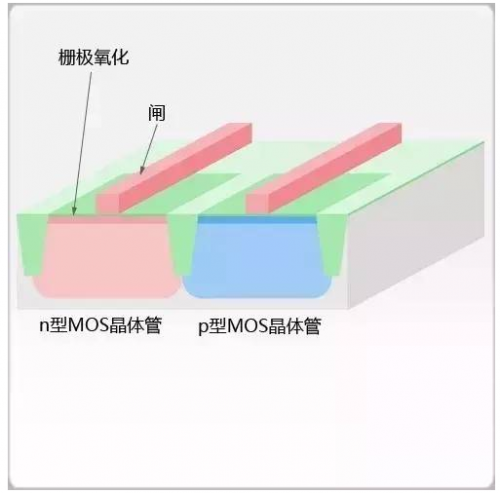

3、栅极氧化及闸形成

这是决定晶体管性能的最重要的工序。 因为栅极氧化影响晶体管的性能及可靠性极大,所以需要在晶片表面形成分布均匀的高密度薄膜。

由于闸形成的尺寸也会对晶体管的性能产生重要影响,因此有必要对光刻胶形成以及栅极蚀刻进行严格的尺寸管理。 并且,利用CVD法来沉积多晶硅可形成栅电极。

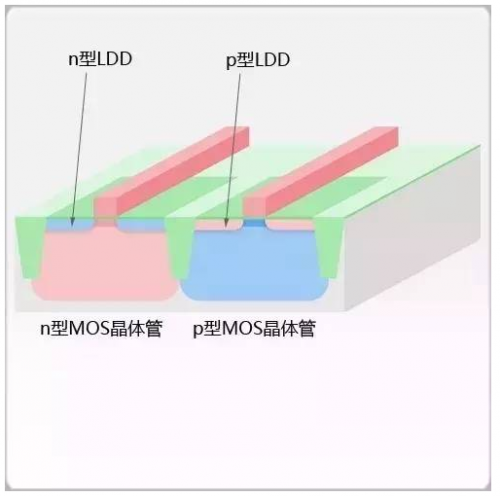

4、LDD形成

LDD(Lightly Doped Drain,轻掺杂漏)的形成是为了避免晶体管微型化带来的不利影响(操作速度变慢等)。LDD也被称为扩展。

n型LDD:在n型MOS的区域内加入n型杂质(如磷,砷等)。

p型LDD:在p型MOS的区域内加入p型杂质(如硼等)。

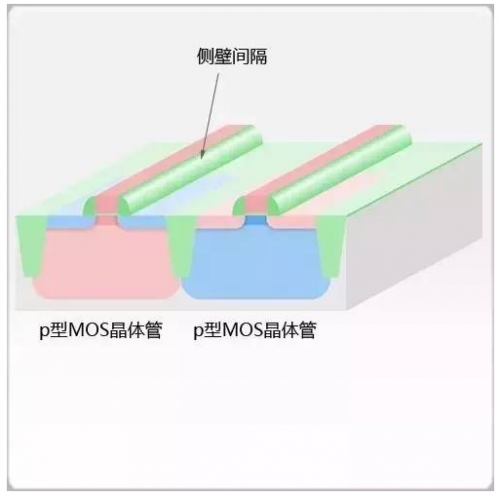

5、侧壁间隔

为形成上述的LDD及,栅极、源极、漏极的硅化(下述),需要仅在栅极的水平方面(两端)的壁部形成氧化膜。

侧壁氧化膜:在整个晶片表面形成氧化膜。

侧壁蚀刻:在氧化膜上实施异向性(垂直方向)的蚀刻,使得氧化膜仅残留在栅极的侧壁。

6、源极与漏极

n型MOS与p型MOS领域内会各自形成源极和漏极。通常情况下,晶体管左右对称,所以形状也相同。电源的连接方向决定哪一端是源极或漏极。

p型源极与漏极:p型MOS区域内掺入p型杂质(如硼等)。

n型源极与漏极:n型MOS区域内掺入n型杂质(如磷,砷等)。

7、硅化物

对MOS的三个电极即栅极(多晶硅)、源极、漏极(硅)进行硅化(与金属的化合物)后,可以降低对金属布线层的电阻。同时,也可以降低各自电极滋生的电阻。

硅化:通过化学蚀刻(自对准硅化),选择性地仅去除钴薄膜。

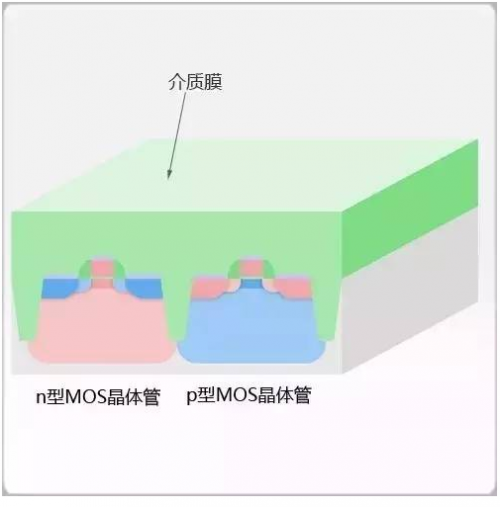

8、介质膜

接下来是连接晶体管等元件的布线流程。

介质膜沉积:通过CVD法形成厚的硅氧化膜等。

介质膜抛光:为使晶体表面凹凸不平的部分变得平坦,对介质膜进行抛光。

9、接触孔

为了将晶体管的三个电极即栅极、源极、漏极透過介质膜之上的金属层相互连接,要对介质膜进行开孔(接触孔)并填充W(钨)。

插件钨填充:於接触孔内填充钨。

插件钨抛光:对表面进行抛光,去除多余的钨,使得钨仅留在接触孔的内部。

10、金属-1

形成介质膜,挖沟槽,於沟槽填充Cu(铜)。 仅向沟槽内填充Cu(铜)的方式也被称为单镶嵌(single damascene)。

金属-1 Cu(铜)填充:通过电镀的方式向沟槽填充Cu(铜)。

金属-1 Cu(铜)抛光:对表面进行抛光以去除Cu膜(铜膜),使得Cu(铜)仅留在沟槽内部。

11、金属-2

形成介质膜,挖孔及沟槽,於孔和沟槽填充Cu(铜)。通过同时向孔及沟槽填充Cu(铜)的方式被称作双镶嵌(dual damascene)。

金属-2 Cu(铜)填充:通过电镀的方式向孔及沟槽填充Cu(铜)。

金属-2 Cu(铜)抛光:对表面进行抛光以去除Cu膜(铜膜),使得Cu(铜)仅留在孔及沟槽内部。

- 富士通半导体与ARM签署全面授权协议(03-07)

- 富士通微电子推出消费电子类快速响应DC/DC转换器芯片(10-17)

- 富士通半导体面向便携设备推出电源管理芯片MB39C326(06-23)

- 用氢燃料电池为IT行业“加油”,富士通大胆尝鲜(07-22)

- 中国半导体业复苏势头显现 期待政策持续支持(09-03)

- 富士通半导体交付55nm创新方案,解本土IC设计之“渴”(06-03)