浅谈处理器核心构架,嵌入应用又有啥新招

下文将比较ARMv7-M与ARMv8-A AArch32的架构特色与差异。

ARMv7-M架构特色

ARM Cortex-M处理器系采用ARMv7-M架构设定,Cortex-M0和Cortex-M0+则采用类似的ARMv6-M架构。

此架构与先前的ARM架构有许多共同的特色,且经过特殊设计,以支援深层嵌入、低成本的即时微控制器应用。所以移除了旧架构的许多功能,但也加入新功能,制造出一个更像类微控制器的程式设计模型。

举体来说,从旧型处理器(像是常见的ARM7TDMI)的变动可总结如下:

.作业模式的数量从七个以上大幅减少到两个:Handler模式和Thread模式。其中一项模式(Handler模式)具选择性优先权限。

.暂存器档经过简化。虽然开放供程式设计人员使用的暂存器基本上仍同样是十六个,旧型架构中所用的备份暂存器复制机制也大幅减少,因此只有Stack Pointer(r13)会在两个作业模式中加以暂存。备份暂存器为选择性使用,甚至可以省略。

.最大的变动在于异常模式。由于一般的微控制器应用可能会有大量的晶片周边中断,所以标准的巢状向量中断控制器(Nested Vectored Interrupt Controller, NVIC)规格会包含在架构中,所有的Cortex-M核心均包含该规格。同样地,异常处理模式已在包含处理常式位址的向量表上加以标准化。内容的储存与回复作业完全在硬体上实作,简化写入中断处理的软体工作,如此可在实作时达到非常低且可预测的中断延迟时间。

.ARMv7-M定义选择性的记忆体保护架构,该架构与某些旧型ARM处理器所用的架构类似。裸机系统或在即时作业系统(RTOS)下运作的系统由于通常不需要虚拟记忆体,因此不支援虚拟记忆体。

.为支援各种即时作业系统的运作和执行,有些标准的晶片周边也会在架构中加以定义,如SysTick Timer。

.为缩小处理器核心的大小,ARMv7-M处理器的运行限缩到只有Thumb指令集(包含Thumb-2延伸),仅执行最小的子集,进而实现最小的核心。

ARMv8-A AArch32特色

Cortex-A处理器采用ARMv7-A或ARMv8-A架构设定。ARMv8-A处理器提供AArch32执行状态,为32位元ARMv7-A架构的向下相容演化版。这些架构可实现专门设计用来支援Linux、Android、Windows等平台作业系统的功能,而这些系统需要虚拟记忆体环境。

其与Cortex-M处理器核心截然不同的特定功能包括:

.有七个以上的作业模式:User、Supervisor、阻断要求(IRQ)、快速中断(Fast Interrupt, FIQ)、Undefined、Abort、System。每一模式皆用于处理特定类型事件(例如IRQ模式便是设计用于处理IRQ中断)。AArch32亦支援Hyp和Monitor这两个额外的模式,这两个模式分别用于虚拟化及ARM TrustZone技术。

.除了可用的登录数量相同(16),AArch32还有许多与上述作业模式相关的"备份"暂存器。进入相关的作业模式时,这些暂存器将取代User模式下的暂存器。如此可简化许多异常处理工作,但也表示机器的管理和初始化工作将增加。

.其异常模式极为不同,其原型存在于最早的ARM架构装置中。具体来说,向量表包含一组可执行的指令集,而不是位址,且内容的储存与回复Restore工作几乎完全交给程式设计人员执行。

.最大的差异是加入了记忆体管理单元,可执行核心所核发之虚拟位址,以及记忆体系统所需要的实体位址间的转译。如此便能实作完全的随选分页虚拟记忆体环境,以供Linux等平台作业系统使用。

ARMv7-M与AArch32的差异

从采用Cortex-M处理器的系统转换到采用Cortex-A32处理器时,有许多新功能值得关注。

虽然这两种架构有许多类似之处(如备份暂存器和指令集之间有许多相同点),但重要的是ARMv8-A架构的AArch32执行状态所含的许多功能,均是以旧型架构的功能为基础。

接下来说明AArch32所具备,但为ARMv7-M所无或差异极大的功能。

作业模式

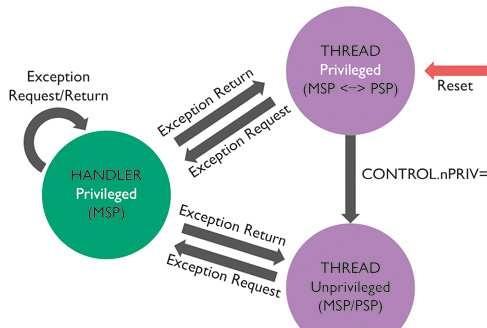

如图3所示,ARMv7-M只定义两个作业模式:Thread模式与Handler模式。若无需要,Handler模式可选择性取消优先权限,虽然这项功能未必须要在软体内使用。Handler模式适用于处理异常,Thread模式则用于使用者处理程序。这两个模式转换基本上是自动的,会在特定事件下发生,如图3所示。例如,发生异常时会自动进入Handler模式,异常处理完成时则会退出Handler模式。SVCall指令为主要的方法,软体用其来进入Handler模式(也可将启用的IRQ设定为待处理状态,以执行Handler)。

图3 ARMv7-M作业模式

图4则显示AArch32执行状态支援的作业模式。与ARMv7-M相较,AArch32有七个基本模式,其中五个指定用于处理特定异常。例如,取得FIQ异常时会进入FIQ模式;若发生未定义指令等情形,会进入

- 细说嵌入式领域的那些专业厂商认证(02-22)

- 嵌入式微处理器将走向何方?(03-09)

- 嵌入式系统与FPGA的最新动向(05-18)

- 2011 TI技术研讨会中国站揭开大幕(09-24)

- 新兴嵌入式产品持续推动传感器快速增长(06-20)

- Cortex-M4致三大嵌入式领域比拼新技术(09-13)