这些年,英特尔、三星、台积电在制程上的恩恩怨怨

小编语:在半导体厂商大呼市场不景气,PC市场疲软,智能手机增长迟缓,宏观经济整体不确定性增强的背景下,晶圆代工市场总营收却仍一路看涨,2015年最新数据还没公布,但这之前全球代工厂连续3年保持16%的总营收增长,不管制程工艺是否能顺利向下一个节点演进,半导体厂商的代工需求仍然存在,而且半导体产业总市场容量仍在不断增长,如果英特尔要真的开放自己的晶圆厂来做代工我们也可以理解……

当有新处理器发布时,制造商都会大肆渲染自家产品的厉害之处。其中制程工艺是除了性能之外他们最注重的,比如更先进制程、更小的纳米等等。目前处理器主要分PC领域的x86架构以及移动数码领域的ARM架构。但是它们都有一个共同点,那就是注重制程工艺。我们以往介绍处理器的时候,一般都是一笔带过。今天我们就详细介绍下制程工艺以及各个半导体巨头的研发实力。

●关于制程工艺,你想知道的

目前制程已经发展到nm(纳米)级别

我们知道谈一个CPU的制程工艺都用一个量化单位来形容或者对比。比如Skylake的CPU采用了14nm制程工艺、曾经引起巨大争议的苹果A9 CPU就采用了两种代工厂,一种是三星代工的14nm制程、另一种是台积电16nm制程。

制程是指IC内电路与电路之间的距离

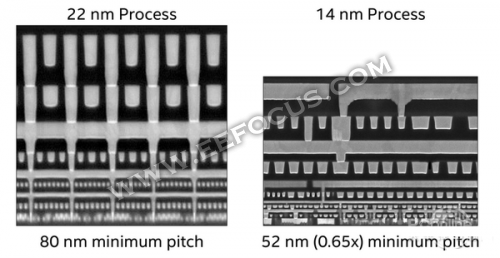

可见,制程的单位是纳米(以前曾用过微米),我们天天说这个距离单位,但是这个距离单位的含义是什么呢?那就是指IC内电路与电路之间的距离。处理器内的微型电子元件(包括晶体管、电容器、电阻器等)躺在方形网格中充当着打开、关闭按钮。电子元件之间的距离就是用纳米来计算。我们都知道,一纳米等于十亿分之一米。电子元件彼此之间的距离越小,我们在芯片中放置的东西就越多。同时同样晶体管数目的DIE面积会降低。

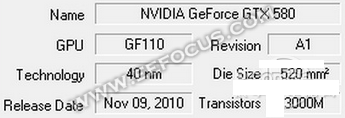

所以,我们看到Geforce GTX 680虽然晶体管数目比GTX 580多,但是芯片面积却只有后者的一半多一点,这就是从40nm制程工艺大幅度进化到28nm的好处。

制程进化的好处:晶体管更多,核心面积更小

同时,制程工艺的进步也带来了理论上功耗的降低。相信大家都在问为什么了,那是因为提升制程,可缩小微处理器电子元件距离。将导致不同晶体管终端电流容量降低,这样就会提升他们的交换频率。每个晶体管在切换电子信号时,其所消耗的动态功耗直接与电流容量相关。所以,制程工艺提升(距离变短)了,同一频率下需求的电流容量降低,耗时也降低,这样晶体管就变得运行速度快、且能耗小。

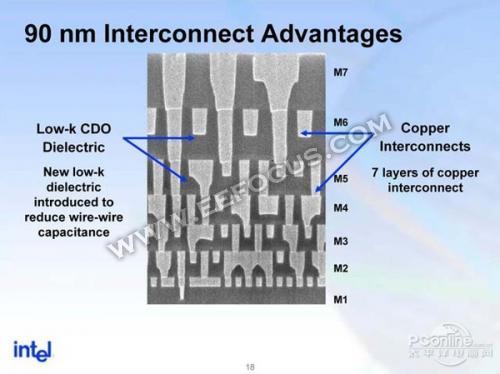

臭名昭著的Intel 90nm制程

当然了,我们加了一个理论上的修饰词,因为只有在同等架构条件下才有这个区分。比如臭名昭著的Intel 90nm制程让Prescott架构处理器被贴上火炉的标签,相比130nm工艺不进则退。原因大家都知道了,就是Intel的优化不足,导致了电压在四方形中发生泄漏,比起平时花了更多的电压来激活通电,于是导致了功耗以及热量的提升。

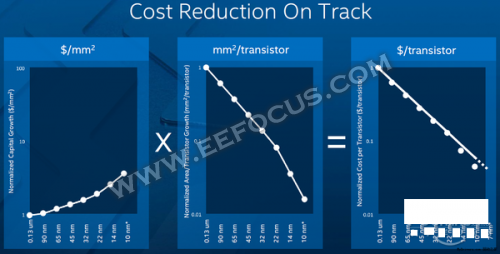

按照这套乘法,晶体管单价会随着制程进化而降低,并且降价幅度越大

我们知道,芯片业界有一则著名的理论,那就是摩尔定律。与其说它与半导体技术息息相关,不如说它是一则经济理论。半导体巨头们为何这么喜欢研发更先进制程?微型电子元件越小,你在晶片所放置的元件就越多。如果你掌握了比同行更加先进的制程,那么在同一面积的晶圆中你就能切割更多数目更小体积的芯片。所以,芯片越小,大成本会越低。尽管更小工艺尺寸需要更多昂贵设备,但这些投资成本会被每个晶片成本所抵消。

说完了一大堆理论,大家明白了制程工艺了吗?下面,我们就简单介绍下各个半导体巨头关于制程工艺的研发实力。

●各大半导体巨头制程工艺发展近况(一)

●Intel

毫无疑问,Intel是半导体工业的技术霸主,是先进制程技术的带头人。

十年来Intel高端CPU核心面积的变化

这些年来,Intel一直坚持Tick-Tock发展模式,新工艺、新架构每年交替到来,从趋势曲线上也可以清晰地看出,每一次升级工艺,核心面积都会骤然缩小,之后再随着规模的扩大而增大,如此往复循环。

14nm让Intel的Tick-Tock发展模式失效

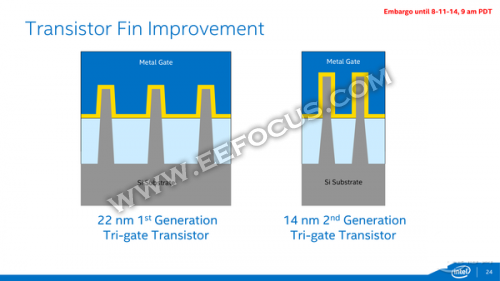

我们知道,Intel发展到Haswell后Tick-Tock发展模式就开始显得有名无实了,那是因为新工艺环节出了问题,也就是在14nm上碰了壁。

原本2013年见面的14nm制程拖到了2014年年底

14nm制程工艺的Skylake四核处理器,可见DIE面积之小

按照Intel内部的预期,2013年底或2014年初,14nm工艺就能登场,结果因为工艺缺陷一拖再拖,直到2014年下半年才登场,而且是拖拖拉拉,最初只有超低功耗版本的Core M系

- 全球芯片库储备或处于危险边缘(02-18)

- 中芯国际第四季财报公布(02-18)

- “中国2011年度电子成就奖”得奖名单揭晓(02-28)

- 2011年1月北美设备订单额小幅下滑(02-24)

- 2011,迷雾中的电子供应链(02-28)

- 英飞凌获德国工业创新奖(02-28)