联发科专家解密Helio X20

联发科于2015年5月发布了集成有10个64位ARM内核的移动产品用应用处理SoC"Helio X20"。联发科设计技术部副总经理Denny Liu通过演讲介绍了这款SoC的开发过程。

图1:Denny Liu发表演讲

Denny Liu是在新思科技、ARM、台积电借第五十二届设计自动化会议之机,于2015年6月8日联合举办的"Collaborating to Enable Design with 16-nm and 10-nm FinFET"上发表的演讲(图1),题目是"Power Scalability : from System to Silicon"。

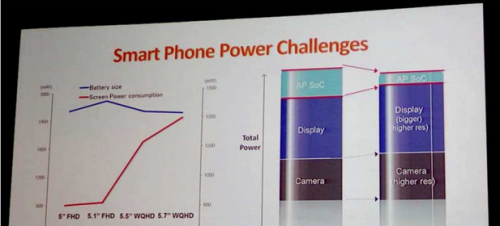

Denny Liu称,最近的智能手机屏幕越来越大,分辨率越来越高,摄像头的像素越来越高,同时外壳越来越薄,电池容量趋于减小(图2)。

图2:应用处理SoC的功耗减小

负责应用处理的SoC也受到了智能手机这一发展趋势的影响。联发科的当务之急是开发比现有应用处理SoC功耗更低的芯片。不过,只是商品目录中功耗值低的芯片还不行,要开发出智能手机用户实际使用时能延长续航时间的应用处理SoC。

3种CPU内核群

因此,联发科按照功耗和性能将智能手机使用的应用分成了三类(图3)。显示待机画面、电子邮件、使用SNS(Facebook等)发送信息等属于"轻度处理",浏览网页、滚动SNS屏幕、播放音乐/录音等属于"中度处理",运行游戏、图像处理相关应用等属于"重度处理"。

图3:将应用分为3种

Helio X20在基本架构上为这三种处理负荷分别准备了CPU内核群(图4)。轻度处理用内核群由4个"ARM Cortex-A53"构成,工作频率为1.4GHz。中度处理用内核群同样由4个Cortex-A53构成,但工作频率稍高,为2.0GHz。重度处理采用了2个比Cortex-A53性能高的"ARM Cortex-A72",工作频率为2.5GHz。

图4:采用3种内核群

功耗降低30%

之所以采用三集群(Tri-Cluster)架构而非通常的双集群(Dual Cluster),是为了更加高效地节能。三种内核群中,用于中度处理的内核群非常重要。联发科利用新思科技的逻辑模拟器"ZeBu",证实了三集群架构的效果(图5)。

图5:评测环境

测试参考了某智能手机用户的应用案例,按照应用,调查了三集群与双集群架构之间功耗的差异。采用三集群后各个应用的功耗有了幅度不同的下降,综合来看,功耗降低了30%(图6)。

图6:评测结果

利用IC Compiler II

Helio X20的布局设计采用了新思科技的自动布局设计工具"IC Compiler II"(图7)。使用该工具,在多存储体、低压工作、DVSF、电源供应等方面容易降低功耗。另外,还有报告称,IC Compiler II的处理时间比上代产品"IC Compiler I"更短,能缩短芯片开发时间。联发科称,IC Compiler II的处理速度是IC Compiler I的5倍。

图7:采用IC Compiler II

Denny Liu在演讲中还展示了台积电微细工艺的效果。Helio X20采用台积电的20nm工艺(N20SOC)制造。据介绍,与28nmHPM工艺(Helio X10采用的制造工艺)相比,N20SOC的速度是其1.2倍,16nm FinFET+工艺的速度是其1.8倍,10nm FinFET工艺的速度是其2.1倍(图8)。另外,在相同速度下,采用16nm FinFET+和10nm FinFET工艺能够降低电源电压,因此可以降低功耗。

图8:微细化的效果

- 芯片供应链:高通MTK“抢食”传统路由(04-07)

- 面霸是怎样炼成的:我的联发科之路(上)(04-15)

- 明年复明年,无线充电一再被“晃点”(10-06)

- IC业集中化趋势加剧,这次的主角是联发科和奕力(07-31)

- 代工厂陷最惨烈一季:台积电、联发科真想跳楼(08-09)

- 瑞昱IC设计逆势增长:大陆,亲人啊(11-11)