基于嵌入式DSP应用的低功耗优化策略

时间:11-02

来源:21ic

点击:

本文结论

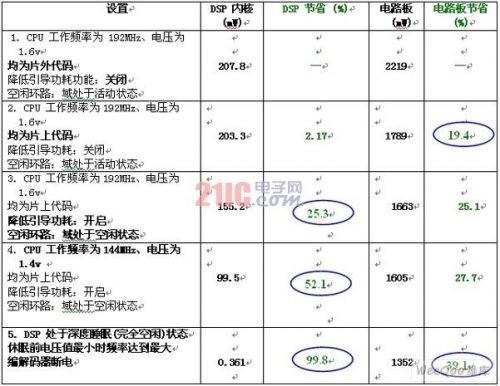

上面的低功耗设计策略的总体效果总结如表1所示,其中:

模式#1为基准测量,全部使用片外代码;

模式#2消除所有片上代码,DSP级节电效果较小,但板级节电达到19%;

模式#3包括一些引导时间节电配置(如关闭DSP的CLKOUT信号、未用计时器的自动空闲配置以及关闭板上LED),以及在BIOS空闲环路中的闲置,从而可实现25%的DSP内核节电;

模式#4为设定点在1.4V的条件下降至144MHz时的功耗,在该模式下可进行音频处理,同时仍能满足实时最低要求,从而实现52%的DSP内核节电;

模式#5为应用处于待机模式下的功耗,该模式配置包括外部编解码器关断、设定点支持以最小电压最大频率快速启动驱动、DSP处于门控时钟深度睡眠模式,该模式下的待机功耗仅为361?W。

设计人员可根据特定应用的要求选择适用的技术。利用OS的这些支持功能,设计人员能够以低开销方便而可靠地提高应用的电源效率。本文讨论的电源优化策略是一种从嵌入式项目之初即可用于降低与调节应用功耗的通用模型。当测量功耗无法满足要求或需要采用额外的运行时技术时,上述策略可重复使用,先期步骤也可重复进行。

- 高性能超声模拟前端AFE5805 (03-18)

- 德州仪器推出低功耗数字温度传感器(05-18)

- TI推出TMP103 数字温度传感器(05-23)

- 德州仪器推出8款65至250MSPS 双通道器件(07-29)

- 小家电能耗不可忽视:耗电量不亚于大电器(08-28)

- TI推出双通道16、14 及 12位数模转换器DAC8562系列(08-28)