绿色处理器设计策略

节能降耗已成为一个社会目标渗透于我们生活的方方面面。由于电子和计算的普及,处理器产业所占全球能耗的份额在不断增加;个人电脑、家用电器和工业设备、大型服务器群,甚至越来越多的智能手机中都大量使用处理器。

对于研发这些电子产品的工程师和设计人员来说,在提供高性能设计的同时,还要将低功耗,这是一个微妙的平衡。半导体设计水平的根本进步显著提高了此类电子电路的能效。为实现节能降耗,过去几年,行业主要关注的一直是多核架构。尽管采用多核架构能够在一定程度上解决功耗问题,但有一种不太知名的处理器设计方法则有望更大幅度地降低能耗。即采用自同步(self-clocking)处理内核的方法。

功耗/性能/成本的权衡

十年前,向更先进工艺节点的迈进是个激动人心的命题,这意味着:更快的时钟速度;每片晶圆上可获得两倍的芯片数;当然还有更低的功耗。随着晶体管几何尺寸业已缩小至其最基本的原子维度,要同时改善产品的性能、成本和功耗这三要素就变得越发困难。设计团队只能对上述三要素中的两项进行优化,而无法同时提升全部三项性能:或者优化能耗和成本而牺牲性能;或者优化性能并以更高功耗换取边际成本的改善。所有这些努力都要在高得多的开发成本,以及增加的设计复杂性和风险这一背景下进行的。这些趋势反过来又导致对复杂SoC的投资回报评估变得更困难。

直到最近,微处理器性能方面的提升一直是通过采用在每个技术节点所能得到的更小、更快的晶体管来提高时钟频率的方法加以实现。架构方面的优化以及增加的数据路径宽度进一步提高了性能,同时降低了内核工作电压和功耗。在90纳米技术节点,晶体管的漏电流成为一个重大挑战。采用低阈值电压的更小的晶体管可以减少芯片面积、增加性能,但是增加的漏电流会导致更高的成本。现在,设计人员面临着艰难的选择:加快时钟频率来提高性能,但要以显著增加功耗为代价;降低功耗,但性能上的提升则很有限,要提升性能,只有使用更多门。

多核架构

目前业界提倡的关键策略是在同一个芯片内放置多个处理器,即多核架构。降低时钟频率会使每个处理器更省电,因此这种方法更环保。

多核处理器已越来越普遍,主要是因为它们具有降低功耗并提高系统性能的能力。显然,两个处理器能比一个处理器做更多有用功,且同时还会比简单地使单个处理器的时钟频率快两倍,从而更省电。这种架构可实现更高能效,但会带来两种主要的副作用:降低了硅使用效率;更高的系统复杂性。

由于多核架构需要复制多个相同的核,所以它实质上是直接以硅面积换取系统性能的提升。因采用更小晶体管带来的缩小硅芯尺寸方面的好处会由于要实现多个核而大打折扣。

传统处理器设计面临的挑战

随着工艺节点演进到40纳米以下,漏电流一直是个问题。增加的另一个挑战是需要管理片上工艺变异。两个关键半导体工艺参数--晶体管阈值电压和晶体管有效长度--的变化可能对设计的性能和功耗产生重大影响。随着制造过程中变异的增加,在这些节点的SoC设计人员必须更加谨慎,并采取降低工作频率的措施,以保证设计不仅能满足性能规范,而且要实现可制造性设计。

在半导体技术演进过程中,另一个广为关注的问题是发热和散热。功耗与容抗以及电压的平方成正比。在90纳米节点之前,随着工艺节点的微缩,开关电压也随之减小,从而降低了功耗。现在,工作电压已接近单个晶体管的阈值电压,不可能获得相应的功耗降低以抵消缩小了的芯片面积的散热需求。

随着半导体工艺技术的发展,在给定面积上放置了越来越多的门,如果每个门的功耗不能相应降低,那么该特定面积内产生的热量将增加。由于封装和散热器的散热能力有限,所以,如果转向较小几何尺寸和更快时钟频率将会很快超出设计的散热能力,从而限制了设计所能达到的性能。在升级到更小工艺节点时,传统的数字逻辑设计方法学遇到的挑战越来越大,这就迫使业界寻找到能同时在性能、功耗和成本三方面带来改进的新解决方案。采用自定时(self-timed)异步架构就是解决这些核心问题的一个办法。

异步设计方法的优势

异步电路可以提供多种优势。理想情况下,该技术可实现最高速的电路;还可被用于获得功耗最低的器件。异步(或无时钟电路)设计方法也可用于开发高性能、低功耗和具有更高硅利用率的处理器。

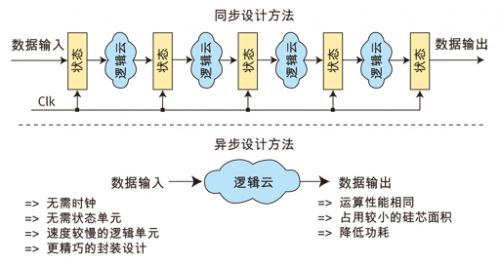

图:采用异步设计方法可以实现更低功耗的处理器电路。

为了解异步电路的优势,首先要将该设计技术与普遍使用的同步方法进行比较。图1所示为一个典型的高度流水线化的处理器设计,由同步实现转到异步实现方法时的综合影响。

去掉了时钟树。同步高速处理器需要大的时钟树来保持序列块的同步。这些时钟树需要大功率缓冲器来驱动覆盖了大部分芯片的复杂高容抗网络。在每一时钟周期,时钟状态改变两次、在上升沿和下降沿都要耗电。这些时钟树不进行任何信息处理、不承当任何有用的计算工作,但它们消耗了总功率的很大一部分。因此,对于高性能处理器而言,仅消除时钟树一项就可降低40%的功耗。

去掉了流水线状态单元。现代的同步高性能处理器高度依赖于流水线设计技术。这些流水线需要非常多的级间(inter-stage)触发器和状态单元以支持高频时钟工作。然而,这些级间触发器和状态单元对于处理器执行的实际数据处理和计算任务并无贡献。在异步设计中,这些存储单元被弃除,从而节省了它们所占用的硅片空间以及大量功耗。

去掉了富余的边沿时序。级间触发器需要设置和保持时间,这就要求在时钟跳变沿之间的这段时间不能用于高频同步设计中的计算工作。此外,由于每一亚微米技术节点的缩微都趋向于增加路径时序的不确定性,这就进一步缩短了时钟边沿之间的有效工作期(active period)。这也意味着,在同步设计中,为执行同样工作,级间电路逻辑需要被设计得比单个时钟周期更快。

这需要在数据路径中更多地使用更大、功率更高的缓冲器。在异步处理器设计中,逻辑没必要处理这么小的时间间隔。可以使用更慢、更小、功耗更低的电路来建构这些逻辑,而且同时还保证了同等整体性能水平。由于门可以慢一些,因此允许更多地采用低漏电、高阈值电压(VHT)门,从而大大减小了漏电流并进一步降低了功耗,缩小了硅芯面积。

缩短了互连线长度。前面谈到的硅片面积的缩小可进一步降低功耗,这是因为随着这些单元间电路的缩微会导致单元间连线缩短。线路越短、容抗越小,因此使用较小的缓冲器对其进行切换所需的功耗也越低。

在处理器实现过程中采用异步设计方法,可以去掉对处理和计算任务没有贡献的时钟树和时序单元。它们还削减了对处理电路的时序约束,从而缩小了面积、降低了功耗。这意味着可采用更少的硅片来完成同等功能,从而降低功耗,因而大幅减小了硅片面积并降低了产品成本。迄今为止,在许多应用中,降低功耗都是极为重要的,这也是设计人员面临的关键挑战。

- 2012年EDA产业趋势预测 SoC功能验证将成为主要议题(01-19)

- 2011年电视半导体市场增长势头减弱,SoC销售额下降(02-13)

- 2011年台湾厂商横扫对手,主宰电视SoC市场(03-01)

- 系统级芯片SoC真的能取代传统CPU?(04-26)

- 欧胜推出业界首款四核高清音频处理器SoC (06-04)

- 实践9号B卫星SoC芯片小如指甲 实现全套大脑功能(11-01)