异质多处理器芯片中的数据流核心设计

异质多处理器系统(Heterogeneous Multiprocessor)是将两种以上不同工作性质的处理器核心整合为一的处理器系统。它通常包含了一般用途处理器(General Purpose Processor)和特殊用途处理器(Specific Purpose Processor)。随着片上系统SoC(System on Chip)及相关技术的成熟,已经可以将不同的处理器整合到一个芯片里,成为多处理器芯片。以多媒体应用为例,比较著名的异质多处理芯片有德州仪器公司的TMS320DSC25、TMS320DM270和TMS320DM320。这些芯片都是由ARM微核心和DSP微核心组成。传统的多处理器系统架构(如Intel SMP架构)是由多个处理芯片通过外部总线汇接而成,而多处理器片上系统架构是在单一芯片上包含了多个处理器核心。它能减少系统的功耗并使整个系统发挥最大的运算效能。

1 硬件平台

本设计采用的硬件平台是德州仪器公司的TMS320DM270,它由两个微处理器核心ARM7TDMI[2]和TMS320C5409[3]组成。采用主从式架构,前者为主动端,后者为被动端。ARM7TDMI是32位的一般用途处理器,负责DM270系统的整体运作和所有周边设备的控制。TMS320C5409为16位的数字信号处理器,主要负责多媒体信号处理,如音视频的编解码运算等。ARM可以经由DSP控制器重置或唤醒,还可对DSP发出不可屏蔽式的中断(Non-Masked Interrupt)。

双处理器之间必须有良好的通信和数据交换机制,才能使系统在多进程环境下有效合作。在DM270中,ARM端的DSP控制器控制数据传输,DSP端通过HPI[3](Host Post Interface)与ARM处理器沟通。两个微处理器使用HPIB(Host Port Interface Bridge)相互连接。ARM和DSP可向对方发出硬件中断,同时它们之间存在一段共享存储区。通过共享存储区映射机制和中断的搭配,双方可以传输信息和数据,并且可以在共享存储区存取双方共同定义的指令,使两端根据指令进行对应的动作。

2 ARM端的DSP管理者

为配合DSP的工作,在ARM端微核心(Micro Kernel)中设计了一个伺服进程,它负责ARM与DSP的沟通及协调运行。该进程称为DSP管理者(DSP Manager),如图1所示。

ARM端的进程并不知道DSP处理器的存在,只知道DSP管理者在运行。当ARM端的进程需要使用DSP进程所提供的数据处理服务时,只需向DSP管理者提出请求。DSP端的进程也不知道ARM处理器的存在,DSP管理者把ARM端的请求存放在共享存储区,由DSP的数据流核心读取这些请求,并交给相应的DSP进程。当请求被DSP进程接收后,DSP管理者还要负责把提出请求的ARM端进程的数据存放在共享存储区,以便DSP端进程的读取和处理。因此ARM与DSP沟通的效能取决于DSP管理者的执行效能。

DSP管理者接收ARM端进程的数据处理请求。请求信息应该包括提出请求的ARM端进程的ID、DSP端服务进程的ID、数据处理服务类型的ID以及相关参数。同时DSP管理者把这些请求信息打包封装为DSP端系统能识别的内容格式,再通过共享存储区交给DSP端的数据流核心。

由于真正维持系统运作的是ARM端系统,DSP只是附属的处理系统,所以ARM端的DSP管理者可以在系统正常工作的情况下更换DSP系统,以支持不同的DSP应用。

3 DSP端的数据流核心

DSP端的系统采用数据流核心(Dataflow Kernel)架构。传统系统核心架构中的进程切换由Timer Tick决定,但数据流核心中的进程却不受Timer Tick的影响,它们以数据驱动(Data Driven)的方式工作。

在DSP端的核心运行着多个不同类型的数据处理服务进程,这些进程在DSP启动时都被设为阻塞态(Sleep)。因为此时没有任何数据可以用来驱动DSP服务进程的执行。当ARM端开始传送数据处理请求到DSP端时,数据流核心会根据这些请求找到对应的DSP服务进程,并使其进入执行态(Busy)。当该服务进程的数据处理任务完成后,其返回结果可能是新的数据处理请求,该请求同样也可以进入数据流核心,驱动其他服务进程的执行。所以整个核心的运行是根据数据流(ARM端的数据和DSP进程自己产生的数据)的动向决定的。与基于Timer Tick的传统系统核心相比,只要某一服务进程不断地接收数据处理请求,并且所需的数据不断到达,该进程就可以一直拥有CPU的使用权,而无须进行时间片方式的进程切换,从而减少了系统资源的浪费,提高了DSP的处理效能。

DSP端的进程有执行和阻塞两种状态。进程的状态转移如图2所示。当CPU使用权切换给某个进程时,该进程的状态将被核心设定为Busy并开始处理数据。当数据处理完后,数据流核心从数据请求队列DRQ(Data Request Queue)中取出下一个请求。如果请求信息中指定的DSP服务进程与目前进程相同,则该进程的状态依旧为Busy,否则核心便将目前进程的状态设定为Sleep,同时开始进程切换,将请求信息中所指定的服务进程设定为Busy。

3.1 进程队列状态寄存器

ARM端系统和DSP端系统在共享存储区共同定义了16位的进程队列状态寄存器(Process Queue Status Register),每一位代表DSP端一个进程的状态,所以DSP端最多有16个数据处理服务进程。若DSP端的数据流核心将寄存器的某一位设为0,则表示与该位对应的DSP进程有能力处理新的数据处理请求;若设为1,则表示与该位对应的DSP进程没有能力处理新的请求。

DSP管理者通过查看该寄存器,可以知道DSP端的某些进程已不能接收新的数据处理请求,它就会使ARM端的相关进程停止向这些DSP进程发出请求。这样可以充分利用DSP的资源,降低DSP端的系统负担。

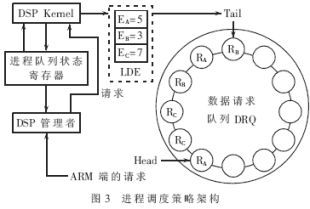

3.2 数据流核心的进程调度策略

核心中的进程调度策略是根据数据流架构上进程运行状态变化的规律设计的。其工作方式是将ARM端对DSP端的数据处理请求利用环行队列(Circular Queue)的架构以FIFO的方式排序,并存入DRQ中。该策略的特点是DSP端的每一个进程都预先指定最多可以拥有DRQ空间的数目,等级越高的进程拥有DRQ使用空间就越多,证明其可以处理更多的数据请求。该策略将传统系统核心中进程优先级(Priority)的概念转化为进程可以处理数据请求的多少。进程等级越高,能处理的数据请求也越多,同时占用CPU的执行时间也较长。LDE(Local Data Element)是DSP端每一个进程都有的参数,它表示DSP进程在执行过程中还可以接收多少个数据处理请求。LDE的初始值由系统定义。整个DRQ空间的大小由所有DSP进程的LDE预设最大值的总和决定。

当DSP端的数据流核心取得ARM端的数据处理请求时,根据请求找到指定的DSP端进程,把该进程的LDE减1,然后进行相应的数据处理。如果LDE被减至0,则DSP端数据流核心把该DSP进程在进程队列状态寄存器中所对应的状态位设为1,以通知DSP管理者该进程不能再接收新的请求,分配给该进程的所有DRQ 空间都已被使用。此后,随着DRQ中的数据请求逐渐被处理,使得该进程的DRQ空间再出现剩余时,数据流核心会把进程队列状态寄存器中所对应的状态位设为0,通知DSP管理者可以再次向该DSP进程发送数据处理请求。

如图3所示,DRQ是环行队列结构,存储所有的请求信息。DRQ有两个指针:Tail指向DRQ没有被使用的空间;Head指向DRQ中将被处理的请求。LDE有三个元素EA、EB、EC,代表DSP的进程A、B、C分别可使用的DRQ个数。数据流核心接收请求RB后,调度算法将EB减1,并且通过Tail指针将请求RB加入DRQ中。当系统需要处理请求时,调度算法由Head指针取出请求并交由适当的DSP进程处理。

- 分析:2011年商用PC市场发展情况乐观(03-01)

- 富士通半导体与ARM签署全面授权协议(03-07)

- ARM手机芯片市场份额已超90% 英特尔倍感压力(03-17)

- 中国正探寻如何快速进驻HPC芯片领域(03-23)

- 美国国家半导体推出10款全新SolarMagic IC芯片 (05-03)

- IDC:中国一季度平板电脑出货量达86万台(07-20)