众多核时代来临:Tilera推出全球首个百核处理器

时间:09-28

来源:与非网

点击:

Tilera引领"众核"时代,在网络、多媒体、无线及云计算应用领域上开辟了崭新的可能。

Tilera公司近日宣布推出新款TILE-Gx™系列产品--四个Tilera最新的处理器,其中包括世界上首个通用百核处理器:TILEGx100™。TILE-Gx100 提供其他尚未公布的最高性能多核微处理器4倍以上的性能。

TILE-Gx 系列产品大大提高了性能功耗比,相比英特尔下一代的Westmere处理器,在相同功耗下提高了10倍的计算效率。此外,Tilera在其突破性的多核开发环境™(MDE)中简化了多核编程, 并通过其快速发展的合作伙伴和生态系统为客户提供产品快速部署的可能。

TILE-Gx 系列--16,36,64和100核芯片采用Tilera的独特iMesh架构,远远超出了传统的微处理器内核的数量。 Tilera的二维iMesh™互连,无需片上总线而其动态分布式缓存(DDC™)系统就可让每个内核本地CACHE,快速的共享于整个芯片。这两项关键技术是目前无法比拟的尖端核心技术,使TILE架构™的芯片性能可以随内核个数而线性增长。

"随着包括世界上第一个100核微处理器的TILE-Gx系列的推出,将开创了一个众核(超多核)处理的新时代。我们相信,这种超多核、超高性能的下一代芯片,将会开创崭新的计算能力," Tilera首席执行官Omid Tahernia说道,"现在,客户可以使用仅仅一个TILE-Gx处理器来替代目前客户使用多个芯片所做的板卡,从而大大简化系统架构, 成本,功耗及PCB板面积。这是一个显著的技术创新成就。"

领导CPU架构向众核的演进

Tilera在可扩展多核CPU架构的突破改变了计算模式。众核处理器开启了广泛的新机会, 包括:

集成计算:单片众核处理器可以集成以前需要多个处理器所能达到的功能,从而降低系统成本,为开发人员提供一个单一的软件工具链和编程模式。 分布计算:用户可以根据单核处理能力,精确地分配资源以实现所规划的功能,达到优化性能和节省功耗。 确定性计算:使处理核专注于某项具体的任务,包括计算的共享高速缓存岛,以实现高度可预测的性能。"在人类微处理器发展史上总有一些关键突破对计算性能产生巨大影响,采用多核技术来克服单核时钟速度上的瓶颈就是一个很好的例子," Gartner公司的首席研究分析师, 瑟吉斯·姆契尔先生说到,"云计算和虚拟化已揭开了一个处理能力优化和广泛运用的新篇章,加速了多核架构的发展进程,实现了从过去时钟频率论的陈旧模式到发展核数量和核优化的新观点。"

关于TILE-Gx 处理器系列

TILE-Gx 系列,采用了台积电的40纳米工艺制造,运行在高达1.5 GHz的时钟,功耗从10到55瓦不等。像TILE and TILEPro™ 处理器一样,TILE-Gx 系列把多个处理核心,高速内存控制器和强大的高速I/O集成到单个芯片里。并且在提供业界最佳的性能功耗比的同时,TILE-Gx 器件汇集了许多新的特性,最大限度地提高了处理器的应用性能。需强调的技术重点包括:

新一代64位处理器核心:单时钟可以执行三条指令的64位处理器,集成完整的虚拟内存系统。每个内核包含着32KB的L1 I-cache,32KB的L1 Dcache,256KB L2 cache和高达26MB的L3 coherent cache。 增强的SIMD指令扩展:单时钟周期可执行四个乘累加(MAC),提供高达每秒6000亿MACs的信号处理性能,超过速度最快的其他商用DSP芯片的12倍的MAC速度。 集成高性能DDR3内存控制器:两个或四个72位DDR3控制器,带有ECC保护功能,运行速度最高可达2133 MHz。可提供高达1TB的DDR3总容量并支持内存条带模式 硬件加速引擎:片上MiCA™(多路iMesh加密加速器)系统提供高达40Gbps的加密和20Gbps全双向数据压缩处理,其无缝连接到iMesh网路,创新地实现了极低的数据延迟和线速流量的小包处理。此外,高性能的随机数发生器(RNG)和公共密钥加速器能达到每秒5万次的RSA交互。 网络包处理加速器:mPIPE™(多核可编程智能包引擎)系统提供线速的数据包分类,负载平衡和数据包缓冲管理处理。这种灵活的,C编程的包处理引擎提供80 Gbps和120M pps吞吐量多层包协议处理。市场定位和供货

TILE-Gx 处理器系列是包括企业网络,云计算,多媒体和无线基础设施在内的巨大市场的理想产品,并通过TILE-Gx16™ 针对成本敏感的应用环境和TILE-Gx100定位高端超高性能的应用。

TILE-Gx36 处理器的样品计划于2010年第四季度面市,其他几款处理器将于之后的两个季度内推出。

欢迎您与Tilera一同参加将在2009年10月28日上午11时至下午5时美国东部时间举行的EE Times 众核虚拟会议, 一起听听来自Tilera和其他公司嘉宾的"大步迈向众核"的相关演讲。 Tilera将会在一个主要的展位上提供关于TILE-Gx 产品系列的详细资料并解答所有参会者可能提出的疑问。 详情请登入:http://www.eetimes.com/manycore/

Tilera公司近日宣布推出新款TILE-Gx™系列产品--四个Tilera最新的处理器,其中包括世界上首个通用百核处理器:TILEGx100™。TILE-Gx100 提供其他尚未公布的最高性能多核微处理器4倍以上的性能。

TILE-Gx 系列产品大大提高了性能功耗比,相比英特尔下一代的Westmere处理器,在相同功耗下提高了10倍的计算效率。此外,Tilera在其突破性的多核开发环境™(MDE)中简化了多核编程, 并通过其快速发展的合作伙伴和生态系统为客户提供产品快速部署的可能。

TILE-Gx 系列--16,36,64和100核芯片采用Tilera的独特iMesh架构,远远超出了传统的微处理器内核的数量。 Tilera的二维iMesh™互连,无需片上总线而其动态分布式缓存(DDC™)系统就可让每个内核本地CACHE,快速的共享于整个芯片。这两项关键技术是目前无法比拟的尖端核心技术,使TILE架构™的芯片性能可以随内核个数而线性增长。

"随着包括世界上第一个100核微处理器的TILE-Gx系列的推出,将开创了一个众核(超多核)处理的新时代。我们相信,这种超多核、超高性能的下一代芯片,将会开创崭新的计算能力," Tilera首席执行官Omid Tahernia说道,"现在,客户可以使用仅仅一个TILE-Gx处理器来替代目前客户使用多个芯片所做的板卡,从而大大简化系统架构, 成本,功耗及PCB板面积。这是一个显著的技术创新成就。"

|

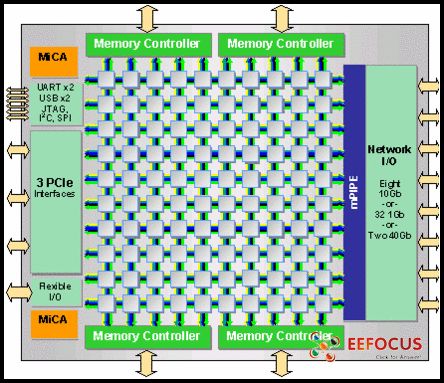

| TILE-Gx系列处理器核心架构图 |

Tilera在可扩展多核CPU架构的突破改变了计算模式。众核处理器开启了广泛的新机会, 包括:

集成计算:单片众核处理器可以集成以前需要多个处理器所能达到的功能,从而降低系统成本,为开发人员提供一个单一的软件工具链和编程模式。 分布计算:用户可以根据单核处理能力,精确地分配资源以实现所规划的功能,达到优化性能和节省功耗。 确定性计算:使处理核专注于某项具体的任务,包括计算的共享高速缓存岛,以实现高度可预测的性能。"在人类微处理器发展史上总有一些关键突破对计算性能产生巨大影响,采用多核技术来克服单核时钟速度上的瓶颈就是一个很好的例子," Gartner公司的首席研究分析师, 瑟吉斯·姆契尔先生说到,"云计算和虚拟化已揭开了一个处理能力优化和广泛运用的新篇章,加速了多核架构的发展进程,实现了从过去时钟频率论的陈旧模式到发展核数量和核优化的新观点。"

关于TILE-Gx 处理器系列

TILE-Gx 系列,采用了台积电的40纳米工艺制造,运行在高达1.5 GHz的时钟,功耗从10到55瓦不等。像TILE and TILEPro™ 处理器一样,TILE-Gx 系列把多个处理核心,高速内存控制器和强大的高速I/O集成到单个芯片里。并且在提供业界最佳的性能功耗比的同时,TILE-Gx 器件汇集了许多新的特性,最大限度地提高了处理器的应用性能。需强调的技术重点包括:

新一代64位处理器核心:单时钟可以执行三条指令的64位处理器,集成完整的虚拟内存系统。每个内核包含着32KB的L1 I-cache,32KB的L1 Dcache,256KB L2 cache和高达26MB的L3 coherent cache。 增强的SIMD指令扩展:单时钟周期可执行四个乘累加(MAC),提供高达每秒6000亿MACs的信号处理性能,超过速度最快的其他商用DSP芯片的12倍的MAC速度。 集成高性能DDR3内存控制器:两个或四个72位DDR3控制器,带有ECC保护功能,运行速度最高可达2133 MHz。可提供高达1TB的DDR3总容量并支持内存条带模式 硬件加速引擎:片上MiCA™(多路iMesh加密加速器)系统提供高达40Gbps的加密和20Gbps全双向数据压缩处理,其无缝连接到iMesh网路,创新地实现了极低的数据延迟和线速流量的小包处理。此外,高性能的随机数发生器(RNG)和公共密钥加速器能达到每秒5万次的RSA交互。 网络包处理加速器:mPIPE™(多核可编程智能包引擎)系统提供线速的数据包分类,负载平衡和数据包缓冲管理处理。这种灵活的,C编程的包处理引擎提供80 Gbps和120M pps吞吐量多层包协议处理。市场定位和供货

TILE-Gx 处理器系列是包括企业网络,云计算,多媒体和无线基础设施在内的巨大市场的理想产品,并通过TILE-Gx16™ 针对成本敏感的应用环境和TILE-Gx100定位高端超高性能的应用。

TILE-Gx36 处理器的样品计划于2010年第四季度面市,其他几款处理器将于之后的两个季度内推出。

欢迎您与Tilera一同参加将在2009年10月28日上午11时至下午5时美国东部时间举行的EE Times 众核虚拟会议, 一起听听来自Tilera和其他公司嘉宾的"大步迈向众核"的相关演讲。 Tilera将会在一个主要的展位上提供关于TILE-Gx 产品系列的详细资料并解答所有参会者可能提出的疑问。 详情请登入:http://www.eetimes.com/manycore/

TILERA TILE-Gx CPU TILEGx100 相关文章:

- Tilera64:主频为900MHz的64核CPU实现量产(09-09)

- Tilera成功融资4500万美元,包括Artis Capital、WestSummit、思科、三星的投资(01-18)

- 台积电满脸“苹果光”(05-06)

- 智能手机陷入“千机一面”怪圈(06-08)

- CPU/APU:一场无声的反垄断技术较量(06-21)

- 移动设备纷纷采用多核CPU遭质疑:性能过剩(01-12)