在EDK中通过IPIF添加用户自定义IP核

时间:03-02

来源:与非网

点击:

1 使用IPIF接口定制用户IP的实现

本例使用IPIF接口定制一个带有中断的视频捕获IP,在制定过程中需要设置用户的IP服务、生成软件驱动程序、添加用户逻辑,以下是定制用户IP的主要过程:

1.1 EDK中添加用户IP通用模板

使用IPIF接口定制用户IP,先要在EDK系统中利用Creat or Import Peripheral 向导创建一个外设IP模板。本例是添加自定义带有中断处理的视频捕获IP(video_capture:截取320*240)。主要IP模板设置过程如下:

1.在向导IPIF Services中依据用户需要设置IPIF的服务,本例需要中断控制获取IP数据,所以需要用户逻辑中断和用户逻辑寄存器的支持。

2..由于本例设有中断,在向导Interrupt Service中要设置需要的中断控制器和中断检测类型,本例只有一个中断并且是上升沿检测,不涉及到中断的优先级,所以只用到IPISC,取消Device ISC的设置。

3.向导User S/W Register 中设置用户需要寄存器个数和宽度,由于采集开始信号、像素数据和场结束信号各用一个寄存器,且像素数据是8位,所以需要3个宽度为8的寄存器。

4.本IP逻辑是用Verilog编写,所以要在向导的Peripheral Implementation Support 中选者创建Verilog用户逻辑,为了便于用户IP逻辑在ISE工程中的调试和获得软件接口帮助,同时选中生成ISE工程和模板驱动两项。

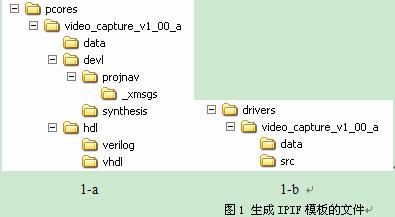

5.点击Next,生成IPIF模板。在用户的工程目录下生成如图1所示目录,pcores目录中含有IP所有硬件信息,drivers目录中包含IP的所以软件信息:

(1)pcores中:data目录包含pao与mpd文件,前者描述了综合仿真需要的文件列表和编译顺序,后者描述了IP核接口信号的名称与特性;hdl目录保存自动生成IP的代码(video_capture.vhd和user_logic.v),分别保存于VHDL和Verilog子目录中;devl目录保存ISE工程相关文件;如图1- a所示。

(2)drivers中:data目录包mdd与tcl文件,前者是描述IP驱动的相关参数,后者提供调用mdd文件定制驱动的命令;src文件夹中就是EDK提供给用户使用的软件驱动,包括驱动模板、函数库,自测程序。如图1- b所示。

实际上这时生成的IP并没有任何逻辑功能,只是一个用户逻辑与MicroBlaze总线的一个接口,IP的逻辑功能需要用户在该生成的user_logic.v文件模板中自己编写。

1.2用户逻辑的实现

编辑用户逻辑有以下几个步骤:

1. 在mpd文件中添加IP外部引脚的声明,可以在这里给IP添加用户需要的引脚,使逻辑电路能与芯片外设或MicroBlaze通信。本例是视频采集模块需要采集CCD的输出信号,所以加引脚如下:

PORT data_in = "", DIR = I, VEC = [7:0] //8位数据输入端

PORT data_out = "", DIR = O, VEC = [7:0] //8位数据输出端

PORT pclk="",DIR=I //CCD像素点时钟输入端

PORT hsync="",DIR=I //CCD行信号输入端

PORT vsync="",DIR=I //CCD场信号输入端

PORT rst="", DIR=I //系统复位信号

2.在verilog和vhdl文件夹中分别是用户逻辑模板和IP顶层文件,前者是用户在模板中添加自己的逻辑,本例就是添加的视频采集逻辑。后者是用来连接Microblaze总线、外设和用户逻辑的顶层接口文件,这里系统自动生成了与总线的接口逻辑,只需要用户将信号连接到指定信号名,大大提高了开发效率和减少程序员的工作量,用户只需要在顶层文件(vhdl文件夹的文件)中声明外围端口并且把用户逻辑例化进来。声明变量、端口及例化填写的位置都有提示(如://--USER port added here),vhdl文件(video_capture.vhd)填加如下:

entity video_capture is

……………

// -- ADD USER PORTS ABOVE THIS LINE ---------------

port

(………….

-- ADD USER PORTS BELOW THIS LINE ------------------

--USER ports added here

rst : in std_logic;

pclk : in std_logic;

hsync : in std_logic;

vsync : in std_logic;

data_in : in std_logic_vector(0 to 7);

data_out : out std_logic_vector(0 to 7);

start : in std_logic;

……..)

IP的逻辑功能需在user_logic.v中编写,文件中有提示 (如: // --USER logic implementation added here处添加)。其他声明变量及端口都有提示填写的位置(如: // --USER ports added here ),填加如下:

module user_logic

( // -- ADD USER PORTS BELOW THIS LINE ---------------

// --USER ports added here

u_rst,

u_pclk ,

u_hsync ,

u_vsync ,

u_data_in ,

u_data_out,

u_start,

irq_end,

// -- ADD USER PORTS ABOVE THIS LINE ---------------

………………….)

但是,多数程序员不希望对这两个文件直接修改。而是希望在projnav中的ise工程中修改和编辑用户逻辑,这样不但符合开发人员的习惯,而且可以进行逻辑综合、编译、调试。检查出逻辑错误和功能是否符合用户要求。如下图2是用Chipscope Pro 逻辑分析仪观察到的采集IP的波形。其中start 是Microblaze控制IP开始采集的有效信号,irq_end是一场结束的判断信号,通知Microblaze采集结束,可以进行相应的处理操作。通过这两个信号可以完成采集与处理的协调工作。

本例使用IPIF接口定制一个带有中断的视频捕获IP,在制定过程中需要设置用户的IP服务、生成软件驱动程序、添加用户逻辑,以下是定制用户IP的主要过程:

1.1 EDK中添加用户IP通用模板

使用IPIF接口定制用户IP,先要在EDK系统中利用Creat or Import Peripheral 向导创建一个外设IP模板。本例是添加自定义带有中断处理的视频捕获IP(video_capture:截取320*240)。主要IP模板设置过程如下:

1.在向导IPIF Services中依据用户需要设置IPIF的服务,本例需要中断控制获取IP数据,所以需要用户逻辑中断和用户逻辑寄存器的支持。

2..由于本例设有中断,在向导Interrupt Service中要设置需要的中断控制器和中断检测类型,本例只有一个中断并且是上升沿检测,不涉及到中断的优先级,所以只用到IPISC,取消Device ISC的设置。

3.向导User S/W Register 中设置用户需要寄存器个数和宽度,由于采集开始信号、像素数据和场结束信号各用一个寄存器,且像素数据是8位,所以需要3个宽度为8的寄存器。

4.本IP逻辑是用Verilog编写,所以要在向导的Peripheral Implementation Support 中选者创建Verilog用户逻辑,为了便于用户IP逻辑在ISE工程中的调试和获得软件接口帮助,同时选中生成ISE工程和模板驱动两项。

5.点击Next,生成IPIF模板。在用户的工程目录下生成如图1所示目录,pcores目录中含有IP所有硬件信息,drivers目录中包含IP的所以软件信息:

(1)pcores中:data目录包含pao与mpd文件,前者描述了综合仿真需要的文件列表和编译顺序,后者描述了IP核接口信号的名称与特性;hdl目录保存自动生成IP的代码(video_capture.vhd和user_logic.v),分别保存于VHDL和Verilog子目录中;devl目录保存ISE工程相关文件;如图1- a所示。

(2)drivers中:data目录包mdd与tcl文件,前者是描述IP驱动的相关参数,后者提供调用mdd文件定制驱动的命令;src文件夹中就是EDK提供给用户使用的软件驱动,包括驱动模板、函数库,自测程序。如图1- b所示。

实际上这时生成的IP并没有任何逻辑功能,只是一个用户逻辑与MicroBlaze总线的一个接口,IP的逻辑功能需要用户在该生成的user_logic.v文件模板中自己编写。

1.2用户逻辑的实现

编辑用户逻辑有以下几个步骤:

1. 在mpd文件中添加IP外部引脚的声明,可以在这里给IP添加用户需要的引脚,使逻辑电路能与芯片外设或MicroBlaze通信。本例是视频采集模块需要采集CCD的输出信号,所以加引脚如下:

PORT data_in = "", DIR = I, VEC = [7:0] //8位数据输入端

PORT data_out = "", DIR = O, VEC = [7:0] //8位数据输出端

PORT pclk="",DIR=I //CCD像素点时钟输入端

PORT hsync="",DIR=I //CCD行信号输入端

PORT vsync="",DIR=I //CCD场信号输入端

PORT rst="", DIR=I //系统复位信号

2.在verilog和vhdl文件夹中分别是用户逻辑模板和IP顶层文件,前者是用户在模板中添加自己的逻辑,本例就是添加的视频采集逻辑。后者是用来连接Microblaze总线、外设和用户逻辑的顶层接口文件,这里系统自动生成了与总线的接口逻辑,只需要用户将信号连接到指定信号名,大大提高了开发效率和减少程序员的工作量,用户只需要在顶层文件(vhdl文件夹的文件)中声明外围端口并且把用户逻辑例化进来。声明变量、端口及例化填写的位置都有提示(如://--USER port added here),vhdl文件(video_capture.vhd)填加如下:

entity video_capture is

……………

// -- ADD USER PORTS ABOVE THIS LINE ---------------

port

(………….

-- ADD USER PORTS BELOW THIS LINE ------------------

--USER ports added here

rst : in std_logic;

pclk : in std_logic;

hsync : in std_logic;

vsync : in std_logic;

data_in : in std_logic_vector(0 to 7);

data_out : out std_logic_vector(0 to 7);

start : in std_logic;

……..)

IP的逻辑功能需在user_logic.v中编写,文件中有提示 (如: // --USER logic implementation added here处添加)。其他声明变量及端口都有提示填写的位置(如: // --USER ports added here ),填加如下:

module user_logic

( // -- ADD USER PORTS BELOW THIS LINE ---------------

// --USER ports added here

u_rst,

u_pclk ,

u_hsync ,

u_vsync ,

u_data_in ,

u_data_out,

u_start,

irq_end,

// -- ADD USER PORTS ABOVE THIS LINE ---------------

………………….)

但是,多数程序员不希望对这两个文件直接修改。而是希望在projnav中的ise工程中修改和编辑用户逻辑,这样不但符合开发人员的习惯,而且可以进行逻辑综合、编译、调试。检查出逻辑错误和功能是否符合用户要求。如下图2是用Chipscope Pro 逻辑分析仪观察到的采集IP的波形。其中start 是Microblaze控制IP开始采集的有效信号,irq_end是一场结束的判断信号,通知Microblaze采集结束,可以进行相应的处理操作。通过这两个信号可以完成采集与处理的协调工作。