嵌入式DSP设计中的功耗优化

对基于数字信号处理器(DSP)的系统而言,优化功耗是一项重要但往往难以实现的设计目标。现在,基于DSP的设备常常把以往各自独立的多个应用结合起来,每一个应用都可能有多个工作模式。要得到这样一个设备的功率分布是非常困难的一件事,更遑论整个复杂的系统。设计人员需要获知尽可能多的最佳信息,以及能够帮助他们优化特定应用之功耗的技术和工具。

幸运的是,近年来,在DSP芯片的设计和制造工艺方面,都在不断推出更先进的功耗降低方法。现在的片上功率优化技术能够提供更多的精细控制和更多的省电模式,以及关于处理器功耗的更完整的信息。更新型的DSP开发工具使设计人员得以更深入透彻地了解系统的功率消耗方式,并通过片上硬件来提供功耗降低技术。

为了让开发人员能够更灵活地控制省电技术,更好地协调众多片上功能间的低功率工作和时序问题,DSP操作系统整合了多项功率管理功能。这些内建功能及工具加上系统设计的精心部署,DSP系统的功耗可得到大幅度降低。

低功耗问题

低功耗对所有的DSP系统都很重要,虽然理由因具体应用而异。在网格供电系统中,降低功率就意味着降低开销、提高可靠性,以及实现紧凑型设计,从而可以在相同的空间中集成更多的功能性,同时需要更少的风扇和其它冷却技术。在高清医疗成像等关键应用产品中,器件工作产生的热量甚至可能导致运行故障,因此,低于设备最大额定值并增加对低功耗的要求是至关重要的。

在便携式电子系统中,低功耗有助于尽量减小系统的尺寸及重量,同时把电池充电后的使用时间延至最长。较小电池的使用可进一步降低系统的规模。更低的功率还有助于避免便携式系统在延时使用期间过热。因功耗降低,手机、PDA、MP3播放器、数码相机和视频摄像机这些电子仪器及其他手持式设备的尺寸都日趋纤小,工作温度越来越低,而充电后的使用时间越来越长。

理解功率分布和芯片资源

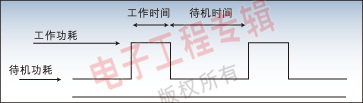

在任何类型的系统中,降低功率的第一步是了解系统的使用方式,以及这种使用是如何影响功耗的。比如,手机大部分时间都处于等待呼叫的状态中,实际通话的时间相当少。另一方面,MP3播放器通常不是开机处于激活运行状态,就是处于关断状态。其它系统、线路供电系统以及便携式系统,都有着不同的待机功耗分布和激活工作功耗分布,参见下面的图1。

图1:工作功耗和待机功耗

了解功耗分布有助于设计人员选择一个具功率效率的处理器,因为在某些类型的应用中,DSP的基本CMOS技术可能对功耗产生很大的影响。先进的CMOS工艺则基于工作电压极低的高性能晶体管。根据既定应用,可以量身定做晶体管,通过对静态电流进行钳位把功耗降至最小,或把性能提高到最大,尽管这样会稍微增加泄漏电流。专门为手机这样的待机时间很长的应用而设计的DSP,可通过低泄漏晶体管把静态电流降至最低,而为总是处于激活状态的高性能应用而设计的DSP则较青睐开关速度更快的晶体管。

系统使用还包括系统对各种事件的响应,以及电路接通电源时的延迟。初始上电时可能有一些延迟,而系统从待机模式被唤醒时,较小的延迟是可以接受的。但用户一般都期望处于激活工作状态的系统能够即时响应,故而这时片上功能不能处于深度睡眠模式。这里有两方面的考虑:第一,部分功能可以较其它功能更彻底地关断,尤其是在待机期间,激活工作期间也如此。第二,处理器的功率模式控制能力越精细,设计人员就越能够进行充分的功耗调节以适合系统的操作情况。

高功率效率的DSP芯片设计通过建立电源域,使应用能够切断不在使用中的功能的时钟输入,从而把所有这些因素都考虑在内了。正如处理内核能够进入睡眠模式,此时它不执行任何操作,直到被中断信号唤醒,外设和存储器模块也同样可以被置于睡眠模式,在需要时才被唤醒。无时钟输入功能中的晶体管除静态电流之外,没有什么功耗,而恢复时钟所需的唤醒延迟被减至最小。系统设计人员在考虑其产品的使用情况时,还需要考虑到在为各项功能提供时钟方面,DSP能够提供多少控制能力,或是否能够自动处理。

节能DSP内建的另一项功能是能够调节核心电压和频率。如果DSP可降低核心时钟速率并仍然满足其处理要求,则工作功耗会相应地按比例节省。更低的频率加上更低的工作电压,可以节省相当可观的能量。可以在系统启动时调节电压和频率以适于整个系统的运行,也可以在应用需要改变时通过软件对之予以动态控制,这就为非峰值处理期间的功耗削减提供了一种重要的手段。

正确功率信息的获

- 首个国产高性能芯片“安徽造”填补国产化空白(03-18)

- 美高森美发布新款高效率以太网供电PoE Midspan产品(02-07)

- 数字电源为FPGA带来高效率(12-16)

- 全球前十大模拟IC供应商 TI再次称霸?(05-25)

- 高通批手机CPU“核战”:优化到位吗?(06-10)

- 德州仪器推出新一代双通道数字音频放大器功率级器件(09-15)