一种多功能存储器芯片的测试系统硬件设计与实现

时间:07-08

来源:3721RD

点击:

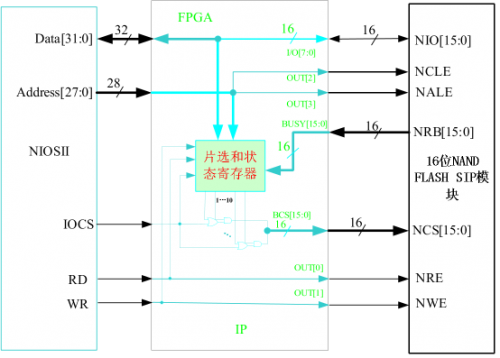

图 4?6 16位NAND FLASH的ABUS接口IP核设计图

验证与总结

将写好的FPGA程序和调试的C代码写入FLASH后,掉电重配置FPGA,串口的输出能正常识别所有设置好的存储器芯片,并能够进行准确地读写功能测试。达到了设计目的。

本文介绍了一种低成本、简单、灵活的多种存储器芯片测试系统的硬件设计,并采用FPGA、FLASH、SDRAM、RS232电路等实现。采用这种方案,用户可根据市场需求,灵活的增加测试系统功能,实现更多的存储器芯片测试。

参考文献:

【1】K9F4G08U0B 512M x 8 Bit / 1G x 8 Bit NAND Flash Memory datasheet,May 30,2008

【2】Avalon Interface Specifications,Version 1.3,August 2010

【3】R1RP0416D Series 4M High Speed SRAM datasheet,Rev. 1.00, Mar.12.2004

【4】HN58V1001 Series 1M EEPROM datasheet,Rev.7.0,Oct.31.1997

【5】MR0A08B 128K x 8 MRAM Memory datasheet,Rev.2,6/2009

【6】S29JL064H 64 Megabit (8 M x 8-Bit/4 M x 16-Bit) datasheet,Revision A,March 26,2004

- ARM硬件设计三:JTAG引脚和PIO引脚(02-27)

- ARM硬件设计四:EBI总线 (02-27)

- ARM硬件设计一:电源和时钟 (02-27)

- ARM硬件设计二:复位引脚和复位期间采样引脚(02-27)

- 嵌入式实时操作系统ECOS在S3C2510上的移植实现(04-21)

- Linux嵌入式系统与硬件平台的关系(03-26)