一种多功能存储器芯片的测试系统硬件设计与实现

SIP存储器测试扩展接口

存储器测试扩展接口在硬件上由两排双排座构成。一共是120个管脚。ABUS接口与测试扩展接口相连接:40个管脚与双向的数据或I/O线相连、8个管脚与8根信号输入控制线相连、16个管脚与16根片选信号输出线相连、5个管脚与5根类别输入信号相连、16个管脚与16根状态输入信号线相连、27个管脚与27根地址线相连。其它的管脚可分配成电源和地线,以及信号指示等。

ABUS接口IP核的设计

每一种SIP存储器对应于一个特定的ABUS接口IP核,以实现正确的时序读写操作。这个IP核有一个统一的接口约定,都是由两个固定的接口构成,其中与NIOSII连接的是外部总线接口,其操作按照NIOSII的外部总线时序规范来实现,另一个接口就是上文提及的ABUS接口,在相应的CLAS信号有效的情况下,它负责把NIOSII的外部总线读写时序转换成对应存储器芯片的时序。IP核的工作就是完成这些读写操作的转换。表5是各种SIP存储器对应的类别信(CLAS)号输入值,在设计接口转接板时要按这个值设定,ABUS才会切换出正确的读写时序。

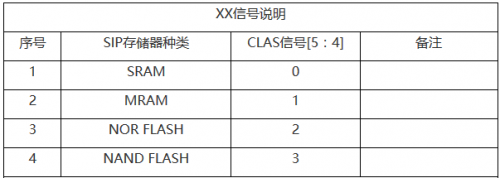

七位类别示别信号含义:T_XX_WW_CC,T为1表示高低测试测试,为0表示常温下的功能测试。XX表示存储器种类,WW表示总线宽度,CC表示容量种类。

表5 各种SIP存储器对应的CLAS信号值

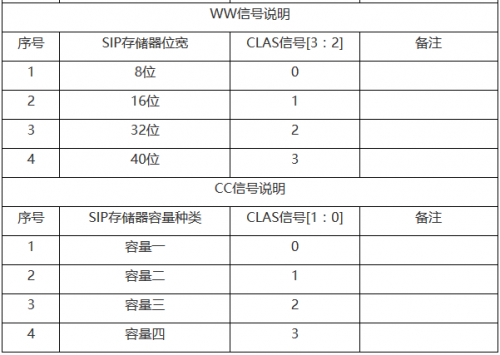

8位SRAM/MRAM/NOR FLASH接口IP核设计

如图4-1,SRAM、MRAM和NOR FLASH的接口操作基本一致,NIOSII的总线时序完全满足。故在FPGA内部只要简单地把相应的控制线和数据线相连就可以了,唯独只要设计一个片选寄存器,用来区分存储器芯片的16个片选。每一个片选可以访问的空间为128MByte。片选寄存器的地址为(基址+0x0FFFFFFC),基地址设在NIOSII外部总线的最高地址位。

图 4?1 8位SRAM/MRAM/NOR FLASH接口IP

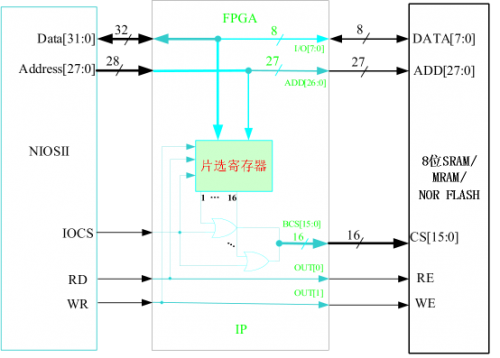

16位SRAM/MRAM/NOR FLASH接口IP核设计

如图4-2,SRAM、MRAM和NOR FLASH的接口操作基本一致,NIOSII的总线时序完全满足。故在FPGA内部只要简单的把相应的控制线和数据线相连就可以了,唯独只要设计一个片选寄存器,用来区分SIP的16个片选。每一个片选可以访问的空间为128MByte。片选寄存器的地址为(基址+0x0FFFFFFC),基地址设在NIOSII 外部总线的最高地址位。

图 4?2 16位SRAM/MRAM/NOR FLASH接口IP

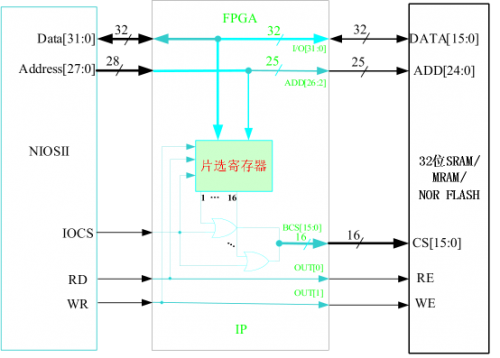

32位SRAM/MRAM/NOR FLASH接口IP核设计

如图4-3,SRAM、MRAM和NOR FLASH的接口操作基本一致,NIOSII的总线时序完全满足。故在FPGA内部只要简单的把相应的控制线和数据线相连就可以了,唯独只要设计一个片选寄存器,用来区分SIP的16个片选。每一个片选可以访问的空间为128MByte。片选寄存器的地址为(基址+0x0FFFFFFC),基地睛设在NIOSII 外部总线的最高地址位。

图 4?3 32位SRAM/MRAM/NOR FLASH接口IP

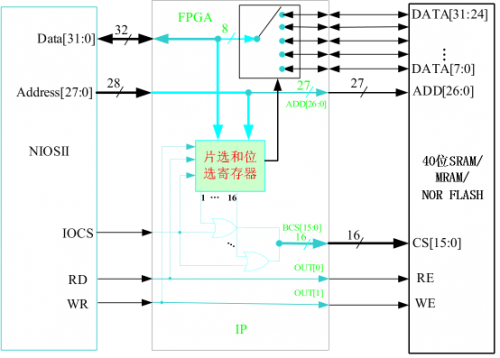

40位SRAM/MRAM/NOR FLASH接口IP核设计

如图4-4,40位的数据宽度有点特殊。在此我们把40位的数据分成5个8位的区域,用8位宽度的总线去分别访问每一个区域。IP核中的位选寄存器就是用来完成切换8位数据总线到40位总线的5个区域的其中一个。片选寄存器的地址为(基址+0x0FFFFFFC),位选寄存器的地址为(基址+0x0FFFFFF8)。最大可以测试128M×40位×16片的存储器SRAM/MRAM/NOR FLASH模块。

图 4?4 40位SRAM/MRAM/NOR FLASH接口IP

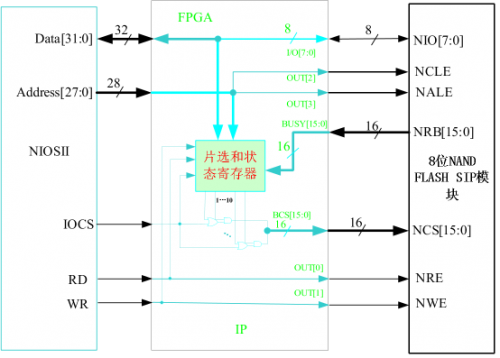

8位NAND FLASH的ABUS接口IP设计

如图4-5,通过写片选寄存器来选中模块的16个片选的其中一个。我们约定其地址为(基址+0x0FFFFFFC)。读状态寄存器返回的是16个NAND FLASH芯片的忙信号,其地址为(基址+0x0FFFFFF8)。向地址(基址+0x00)写入数据就是对NAND FLASH数据寄存器的写操作。向地址(基址+0x00)单元读数据就是对NAND FLASH数据寄存器的读操作。向地址(基址+0x01)写入数据就是对NAND FLASH命令寄存器的写操作。向地址(基址+0x02)写入数据就是对NAND FLASH地址寄存器的写操作。

图 4?5 8位NAND FLASH的ABUS接口IP核设计图

16位NAND FLASH的ABUS接口IP设计

16位的NAND FLASH存储器芯片可以有多种组合方式,可以用多个16位的NAND FLASH组合,也可以用多个8位的NAND FLASH组合。这里我们假设16位的SIP NAND FLASH产品是由多个16位的NAND FLASH组合而成,下面的IP核是根据它的结构来设计的。

如图4-6,通过写片选寄存器来选中模块的16个片选的其中一个。我们约定其地址为(基址+0x0FFFFFFC)。读状态寄存器返回的是16个NAND FLASH芯片的忙信号,其地址为(基址+0x0FFFFFF8)。向地址(基址+0x00)写入数据就是对NAND FLASH数据寄存器的写操作。向地址(基址+0x00)单元读数据就是对NAND FLASH数据寄存器的读操作。向地址(基址+0x01)写入数据就是对NAND FLASH命令寄存器的写操作。向地址(基址+0x02)写入数据就是对NAND FLASH地址寄存器的写操作。

- ARM硬件设计三:JTAG引脚和PIO引脚(02-27)

- ARM硬件设计四:EBI总线 (02-27)

- ARM硬件设计一:电源和时钟 (02-27)

- ARM硬件设计二:复位引脚和复位期间采样引脚(02-27)

- 嵌入式实时操作系统ECOS在S3C2510上的移植实现(04-21)

- Linux嵌入式系统与硬件平台的关系(03-26)