基于多IP核复用SoC芯片的可靠性研究

时间:07-02

来源:3721RD

点击:

|

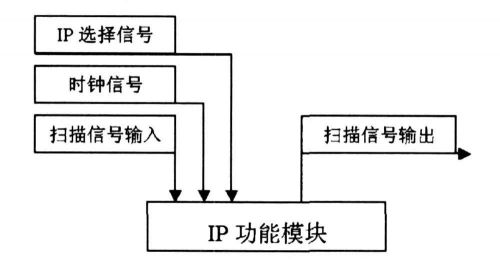

| 图5 |

SoC 芯片在上电运行中自动对自己的运行状态进行监控, 并通过扫描输出信号即时返回该IP功能模块的状态信息, 在其它控制模块中再根据这些状态信息采取相应策略保证SoC 的可靠运行。

3 结束语

对于SoC 芯片, 可靠性是首要考虑的问题, 基于多IP复用SoC 的设计技术, 重点解决处理器的可靠性、多IP核间通信的可靠性、IP核工作异常状态研究, 可以进一步提高SoC 芯片的可靠性。

近几年来本单位根据智能终端产品特点, 进行智能终端专用SoC 芯片研发, 在SoC的设计过程中充分考虑了其可靠性, 加入了非常全面的可靠性算法, 采用奇偶校验、TMR(三模冗余)寄存器、片上EDAC、流水线重启和强迫CACHE 不命中等多层次容错机制来提高SoC的可靠性, 已在FPGA 验证平台上得到验证, 并进行SoC 芯片流片和批量生产验证, SoC 芯片的可靠性得到大幅度提高, 验证本方法可行, 具有很好的推广价值。

相关阅读:

可复用SPI模块IP核的设计与验证

基于IP的智能传感器SOC设计

- 高带宽嵌入式应用中SoC微控制器的新型总线设计 (02-02)

- SoC前段(ARM)嵌入式系统开发实作训练(上) (02-28)

- SoC前段(ARM)嵌入式系统开发实作训练(下)(02-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 开放源码硬件简史(05-21)

- 可配置处理器技术优势详解(05-15)