基于ARM9的SD/MMC卡控制器的ASIC设计

或者读取指定个数的数据块。

读数据过程中,如果卡检测到错误,如超出范围,地址对齐错误等,卡会停止数据发送,停在sending-data状态,控制器需要发送停止传输命令,此时,卡会将错误信息,通过响应返回给控制器。

控制器可以对卡持续进行写数据操作,直到向卡发送停止传输命令;或者指定个数的数据块写完。写数据过程中,如果卡检测到错误,如写保护,地址超出范围,地址对齐错误等,卡会停止数据的接收,停在Receiving-data状态,控制器需要发送停止传输命令,此时卡会将错误信息,通过响应包返回给控制器。一个数据块写完后,卡需要一段时间将这块数据写到内部Flash中,控制器需要查询卡的状态,等卡写完数据后,才能发送下一个命令。

2.4 CRC的算法设计

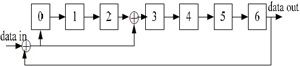

在CMD控制模块和DATA控制模块中均用到CRC校验。CMD控制模块中用的是CRC7,其公式是G(x)=x7+x3+1。实现其算法的逻辑图如图3。

图3 CRC7生成逻辑

在DATA控制模块中用的是CRC16,其公式是G(x)=x16+x12+x5+1。算法逻辑图同CRC7类试,这里我们不再赘述。

两种校验本质相同,后者精度更高,适应数据尤其是长数据的传输校验。

3 功能验证与综合

使用Mentor公司的ModelSim软件进行仿真,该软件许可在PC、Solaris、HP-UX或Linux平台上使用,支持VHDL或Verilog硬件描述语言(HDL)仿真。它支持所有器件的行为级仿真和VHDL或Verilog仿真激励。

为了测试设计的正确性,编写了testbench模块,其中包括一个用HDL描述的SD卡的原型(使得控制器能够对该卡进行操作),包括产生时钟信号,输出命令,读写的数据,产生的中断等。下面以测试SDMMC读写寄存器,发送命令接收响应,4线块数据(block data)传输等为例来说明:

当满足片选信号后,APB总线对内部寄存器先进行配置,然后确定命令的发送,并附上CRC7的校验码,最后接收响应和响应的CRC7校验码。

对流传输,单块,多块数据等所有传输方式进行完仿真,利用目前业界最流行的综合工具:SYNOPSYS公司的DesignCompiler对其综合。经过对Script脚本约束的设定,通过DC将控制器的时序和面积进行优化,工作频率满足手机基带芯片频率125Mhz(最高可到200以上),面积在3万门,比主流的4万门有所降低,节省了面积。

最后采用Xilinx公司的xc4vlx200-10ff1513芯片进行FPGA验证,测试结果表明该控制器可以对市面上主流SDMMC卡进行数据传输,符合整个SOC的要求。

4 结语

验证结束后,利用中芯国际的0.13um的工艺库对上面的设计进行封装制造,就实现了最新的SD1.0和MMC3.31协议,并将其嵌入到ASIC中,使得TD终端具有外部扩展存储性,节约用户开销。不仅如此,该控制器可作为一个成熟的IP核,移植到各种基于多媒体处理的ASIC芯片中去,其应用十分广泛。

作者创新点:该IP核的设计,为TD-SCDMA终端基带芯片以及类似手持SOC提供外接扩展存储卡的功能,且具有广泛的可靠移植性用于其他芯片中。

- 通讯硬件接口综述(11-11)

- 手机自动售货机的嵌入式系统设计(11-19)

- DDR SDRAM在嵌入式系统中的应用(02-07)

- DSP中的存储器共享与快速访问技术设计(06-28)

- 利用 Xilinx FPGA 和存储器接口生成器简化存储器接口(07-27)

- 使用 Virtex-4 器件实现的 DDR2 的控制器(08-03)