基于ARM9的SD/MMC卡控制器的ASIC设计

0 引言

如今多媒体数码产品的迅猛发展,其中,各种音频视频等功能的不断增强,使得系统对于存储介质的性能,容量,安全等方面的要求与日俱增。MMC卡和SD卡均是基于flash的存储设备,近年来,它们以高存储容量,快速的数据传输速率,加上极大的移动灵活性和更高的安全性已经成为闪存市场的标准,其广泛应用于手机,MP3,MP4,掌上电脑等各种产品中。可见,其已经成为面向便携式数码电子产品的SOC芯片中通用的功能接口。

文章设计的SD/MMC控制器基于一款3G手机基带芯片,其内核采用ARM926EJ,系统总线架构为AMBA,控制器连接到APB总线上。通过分析SD卡和MMC卡的规范,利用Verilog HDL实现了符合该规范的SD/MMC卡控制器IP核,该IP在SMIC的0.13um标准单元工艺库下对模型进行了综合和优化。

1 SD/MMC卡控制器工作原理

SD(Secure Digital)卡和MMC(Multi Media Card)卡是市面上常见的两种数据存储卡。SD卡向下兼容MMC卡。

两者基本特性相同,只是在数据接口以及传输模式上有一些区别:SD卡的数据线为4根,而MMC卡只有1根;SD卡支持安全性保护;而MMC卡支持比特流传输(不限长传输,即必须接受到停止命令时才停止传输)。

控制器就是通过SD/MMC总线对SD/MMC卡进行初始化,读,写等一系列操作。其总线包括时钟线CLK,命令线CMD,数据线DAT3-DAT0(MMC卡只有DAT0)等。上电后,控制器必须按一定的总线协议传输命令给卡,使其初始化。总线上一共有三种数据格式:命令包,响应包,数据包。由于在传输中数据和命令均有可能出错,命令带有7位的CRC校验码,数据带有16位的CRC校验码。

控制器对卡进行读操作时,将接收到的串行数据(可能是比特流,也可能是多块)转换为并行数据,存入FIFO。写操作也是相同的,控制器将并行数据从FIFO里面取出,串行发出。

SD/MMC卡的工作时钟来源于控制器,对卡的命令或数据传输等一系列操作均要与该时钟同步。该时钟可以通过控制器进行配置,以适应不同工作状态中卡正常工作所需的不同时钟频率。需要注意的是,SD卡的最大工作频率是25Mhz,MMC卡的最大工作频率是20Mhz.

总之,控制器不仅要输出合适的工作时钟,还要完成对命令/响应以及数据读写的正常工作,并针对命令和数据进行CRC校验,中断的及时产生和清除。

2 控制器设计与实现

2.1 模块划分

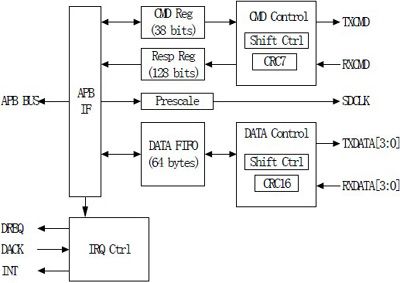

在整个SOC中,我们这片TD基带芯片采用的是ARM926EJ-S内核,系统架构为AMBA总线。在设计中,将SD/MMC卡控制器作为APB的SLAVE挂在APB总线上,ARM通过APB总线来访问和控制该模块。本模块主要分为接口模块,CMD控制模块及DATA控制模块三部分。其结构框图如图1所示。

图1 SD/MMC控制器结构

接口模块实现与ARM的APB总线相连接,通过该模块,ARM可以对相应寄存器进行读写,从而实现对本模块和外部存储卡的控制。其读写时序按照APB总线读写时序,具体见文献。

CMD控制模块主要发送和接收CMD线上的信号。控制器发送给卡的命令长度固定为48bit,而从卡接收到的响应长度不固定,有短应答(48bit)和长应答(136bit)之分。

其中,包含CRC7的子模块,不管是命令还是响应,均要用到CRC校验。

DATA控制模块主要是通过RXDATA数据线接收数据,并通过TXDATA发送数据。主要的数据传输方式有两种:比特流数据传输和多块数据传输,另外,该控制器还支持无响应包数据传输。为确保传输的正确,包含了CRC16校验的子模块。

2.2 CMD控制模块的设计

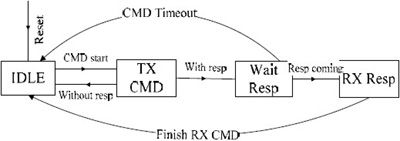

由于SD/MMC卡的操作命令不一致,在模块中并没有对命令作译码,而是通过软件来设置命令的类型。单块(signalblock data)读数据命令(CMD17),写数据命令(CMD24);多块(multi-block data)读数据命令(CMD18),写数据命令(CMD25)等需要控制模块根据SD_CMD_INDEX寄存器的内容来发布相应的命令,并作不同的状态转换。CMD控制模块的状态转换图如图2所示。

图2 CMD控制模块的状态转换

2.3 DATA控制模块的设计

本模块主要功能是向卡发送数据和从卡读取数据,另外,针对SD卡该模块可以通过DATA[3]检测卡是否插入,通过DATA[2]发送读等待信号,通过DATA[1]接收卡送来的中断信号以及通过DATA[0]来检测卡是否处于忙状态。

APB总线上还有其他一些功能模块,如SPI接口控制器,CAMERA控制器等,由于不能一直占有总线,在对卡进行读写的同时,来不及处理及时收到的数据或来不及获取新的发送数据,所以我们采取数据缓存,添加一个64bytes的FIFO。

控制器对卡进行读操作时,需要先发送CMD9命令,获得卡的CSD寄存器数据,其中包含了卡的数据长度,卡存储容量,卡最大时钟速度等。控制器可以持续进行数据读取,直到向卡发送停止传输命令;

- 通讯硬件接口综述(11-11)

- 手机自动售货机的嵌入式系统设计(11-19)

- DDR SDRAM在嵌入式系统中的应用(02-07)

- DSP中的存储器共享与快速访问技术设计(06-28)

- 利用 Xilinx FPGA 和存储器接口生成器简化存储器接口(07-27)

- 使用 Virtex-4 器件实现的 DDR2 的控制器(08-03)