USB设备控制器端点缓冲区的优化设计

方案都是采用双FIFO来实现双向传输的。一个FIFO用以接收主机发送过来的数据包;另外一个FIFO用以向主机发送数据包。在传输数据包时总有一个FIFO处于空闲状态,这样会造成存储器资源的浪费。为此,本文提出一种新型的异步FIFO结构,该结构使用一块双端口sram来实现控制端点的单工双向传输,而传统的双FIFO结构需要两块SRAM用来实现双向传输。由于SRAM占据了FIFO的大部分面积,在实现控制传输的功能下少用了一块SRAM,可以预见最终的电路实现面积会减小将近1/2。

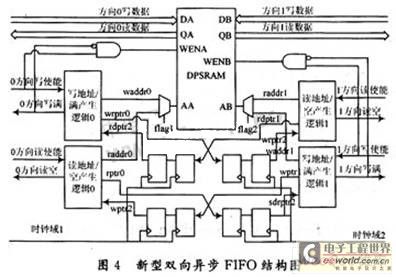

图4是本文所设计的新型异步FIFO结构,该FIFO的实现是基于一块双端SRAM。在上文所提到的异步FIFO结构的基础上增加一套读写指针逻辑和满空判断标志。这个电路可以看作是原来电路模块的复制,即两者设计完全一致。这两个新增的指针模块用以产生访问SRAM的地址和用以产生满和空的格雷码指针。这样在同一方向对于SRAM的访问就会有两个地址,其中一个是读地址,另一个是写地址。这样需要设计一个选择器,用以选择当前访问SRAM的是读地址或写地址。这个选择器的选择端可以根据不同方向的读写使能信号来切换。这是由于在同一时刻不可能出现一个方向的读/写使能均有效的现象。

对于图4的数据路径可简介如下,方向0在其写使能信号的控制下,往FIFO内写入数据,写满之后方向1控制其读使能将方向0写入的数据读出来。然后方向1控制其写使能将数据写入双端口SRAM,方向0负责把SRAM内的数据读出。

对于USB的控制端点,其接收的最大数据包为64 b。故本文设计的双向FIFO使用的sram亦为64 b。使用memory complier生成。图5是设计的双向FIFO在Modelsim下的仿真波形图。该波形显示了方向0写数据,方向1读数据和方向1写数据,方向0读数据的过程。

2.2 其他端点的优化设计

对于USB设备控制器的其他端点,由于其与控制端点有所不同。控制端点是一个双向端点,而非控制端点单向的传输。故对于非控制端点对应的缓冲区的容量设定,应使USB的带宽利用率尽量达到最高。由于USB规范中规定缓冲区必须有足够的空间,可以为全(高)速设备容纳一个时间片所能传输的数据量的两倍的容量。这样USB在处理一个数据分组的同时,可以接收下一个数据分组。以此种重叠技术可以提高总线利用率。如果批量端点的缓冲区的深度设计为1 024 B。就可以得到最大的带宽利用率。

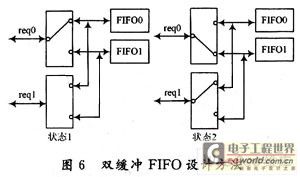

图6是其他端点所采用的双缓冲FIFO方案示意图。在状态1,req0控制访问FIFO0,reql控制访问FIFO1;在状态2,req0切换到访问FIFO1,req1切换到访问FIFO0。基于双缓冲FIFO的设计方案可使其他端点的带宽利用率达到最高,满足高速传输的需求。

3 电路的ASIC实现结果

对上述设计方案采用Verilog硬件描述语言进行设计。仿真工具为Modelsim SE 6.2b,前仿真通过后,对设计好的电路使用Design Complier进行综合。综合所使用的工艺库是SMIC 0.18 μm工艺库。

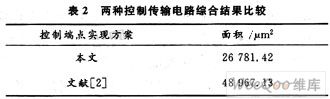

对于控制端点,考虑到其主要处在SIE时钟和MCU时钟之间,对其所加的时钟约束分别为60 MHz和30 MHz;此外还对传统的双缓冲FIFO结构进行了综合,两者所加约束完全一致。将两者的电路的综合结果对比如表2所示。

对比表2可知在保证控制端点功能的前提下,本文所采用的新型FIFO结构比传统双FIFO结构在电路的实现面积方面减小了45.3%。

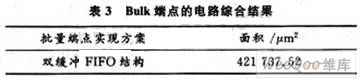

对于其他端点所采用的双缓冲FIFO方案保证了传输速度,但却是以牺牲面积为代价换来的。表3给出了批量(Bulk)传输端点(两个深度为512 B的FIFO)的实现面积报告。

4 结 语

USB设备控制器端点缓冲区的性能,直接关系到总线的带宽利用率。这里分析了USB的四种传输类型并根据其特点灵活的设计了不同的方案,并给出了最终电路的ASIC实现结果。特别是针对控制端点所提出的一种新方案具有一定的通用性,该方案可以应用在其他类似场合的设计中。

- USB设备的调试与测试技巧(11-11)

- USB系统结构与应用设计(01-18)

- 基于C8051F320 USB接口的数据采集存储电路(01-18)

- 基于USB的CAN总线适配器设计(01-21)

- 带USB接口的短信收发最小系统设计(01-23)

- 基于USB总线和Aduc831单片机的数据采集系统的设计(01-25)