USB设备控制器端点缓冲区的优化设计

2000年发布的USB 2.0规范,将USB接口的传输速度提高了40倍。传输速度的提升使得USB设备控制器的设计指标也随之提高,虽然协议中对于缓冲区的设计要求并没有本质上的改变,但是由于总线带宽与传输速度的提高,各个芯片供应商均推出了自己的缓冲区设计方案。为了提高USB接口的数据存取速度,通常使用异步FIFO来设计端点缓冲区。这里首先简要介绍USB中端点的概念,并给出一款异步FIFO的设计方案。然后根据USB四种传输类型的特点,提出基于该FIFO结构的不同类型的端点缓冲区的设计方案。特别是对于控制端点提出了一种新型的双向异步FIFO结构,在保证控制传输的前提下,减小了将近1/2的电路面积。最后给出在Synopsys平台下电路的VLSL实现结果。

1 USB协议中的端点及实施方案

1.1 USB设备的端点

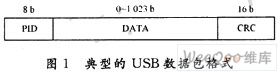

USB主机和设备之间传输的数据是以信息包的格式来传输的,可分为令牌包、数据包、握手包和特殊包。在数据包中包括了主机和设备通信的数据分组。图1是一个典型的USB数据包的格式。

PID域是为了增加USB通信的健壮性而设定的数据分组的辨识符;CRC16域是对数据分组进行CRC校验的结果。DATA域是实际传送的数据内容。USB设备控制器会将接收到的主机数据包放入指定的端点缓冲区;或者从指定的端点取出待发送的数据组装成USB信息包发送到主机。

由此可见,所谓端点实际上是主机与设备之间通信的来源或目的,所有的传输都要传送到设备的端点,或是由设备的端点发出。一系列相互独立的端点在一起就构成了USB逻辑设备。从物理层的角度来看,端点是一块存储器区域,用以缓冲实际接收到或待发送的数据包。

USB协议中定义了四种传输类型,分别是控制传输、批量传输、中断传输和同步传输。所有USB设备控制器都应该支持控制传输,其他三种传输方式根据不同的应用背影而用于不同类型的设备。按照传输类型可将端点分为控制端点、批量端点、中断端点和同步端点。其中控制端点较为特殊,只有它可以双向的传输数据,而其他端点只能传输单方向的数据。

1.2 使用异步FIFO设计USB端点

由于USB设备控制器的缓冲区空间是对应各个不同的端点。每个端点所对应的传输方式、传输方向也不同。通常控制端点会连接控制器的MCU单元,而其他类型的端点一般连接设备端的接口。可见USB的端点缓冲区实际上是在串行接口引擎时钟和设备时钟或MCU时钟的两个时钟域之间传输数据。而使用异步FIFO来实现该结构显然是一个不错的选择。

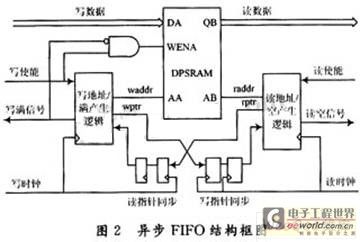

图2是本文所采用的异步FIFO的结构框图。该异步FIFO由一块双端口SRAM、写地址/满逻辑和读地址/空逻辑、以及为了消除亚稳态的两级同步电路组成。左端口在写时钟下进行数据的写入操作;右端口在读时钟下实现数据的读出操作。

对于异步FIFO的设计,产生准确的空满标准是设计中的核心任务,它与FIFO是否能稳定工作息息相关。写满不溢出,读空不多读是异步FIFO空满标志判断的基本原则。传统的判断方法是另外设置一个状态位,作为最高位,其余位作为地址位,当读写指针的地址位和状态位全部吻合时,FIFO处于空状态;当读写指针的地址位相同而状态位相反,FIFO处于满状态。这种异步FIFO由于是通过直接比较二进制读写指针来判断满和空的,在跨时钟传递时会有毛刺产生。下面将介绍一种通过直接比较格雷码指针的方法生成FIFO的空满信号,从而消除了毛刺,提高了电路的稳定性。

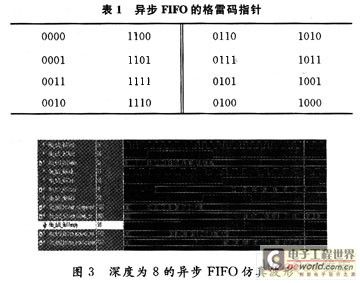

比如要设计一个深度为8的异步FIFO,需要使用3 b的格雷码计数器对读写指针计数,与二进制类似,还是需要使用一个状态位来判断满和空状态。此时FIFO的格雷码指针跳变情况如表1所示。

观察表1可知,当读指针为4’b0011时(二进制为4’b0010),此时比他多一个周期所对应的格雷码为4’b1111(二进制为4’b1010)。两者的高二位恰好相反,但低位完全相同。对比表1左右两列可知当读写指针相差一个周期即FIFO满时对应的格雷码指针的最高两位相反,而低位则完全相同;当两者完全相等时对应为FIFO的空状态。图3给出的是在设计的FIFO的深度为8时,在Modelsim中的仿真波形。由图3可知,当FIFO从空到满时,对应的格雷码写指针为4’b1100,而同步后的读指针为4’b0000;当从满被读空时,读指针为4’b1100;由此可见仿真的FIFO的空满信号与设计一致。

2 基于FIFO结构的优化端点设计方案

2.1 基于新型FIFO结构设计控制端点

上文已经论述过控制端点是一个双向传输的端点,但是在同一时刻只能是单向的数据传输。该端点主要是用于USB设备的枚举过程,主机发送一个信息包,设备负责回应一个信息包。对于该端点的设计现有的

- USB设备的调试与测试技巧(11-11)

- USB系统结构与应用设计(01-18)

- 基于C8051F320 USB接口的数据采集存储电路(01-18)

- 基于USB的CAN总线适配器设计(01-21)

- 带USB接口的短信收发最小系统设计(01-23)

- 基于USB总线和Aduc831单片机的数据采集系统的设计(01-25)