一种基于AT25T1024 FLASH的高速SPI接口设计

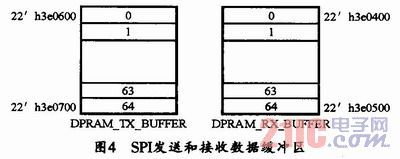

SPI发送数据缓冲区深度65,数据位宽32位,其中地址22’h 3e0600存放访问AT25F1024存储器的指令,当进行写操作时,从数据发送缓冲区最低位地址22’h3e0604开始,将数据搬运出来,串行发送到AT25F1024存储器。

SPI接收数据缓冲区深度65,数据位宽32位,其中地址22’h3e0400缓存读取的AT25F1024配置和状态信息,偏移地址22’h3e0404~22’ h3e0500缓存指定FLASH读取的总线配置数据数据,最大缓存2048位。

3 数据搬运时间

3.1 主机写片外FLASH的时间

本设计使用的存储器AT25F1024缓冲数据寄存器大小2048位,写使能需要8个串行时钟周期,向片外FLASH传输2048位数据需要2080个串行时钟周期(包括了32位写指令的传输数据),这样写一次需要时间为2088个时钟周期,主机将1Mbits的FLASH填满,时间大约为2088 x50ns(串行时钟40/2MHz)×512 (填满1Mbits需要512次写操作)=53.4ms。读1Mbits的FLASH需要的时间约为2080x50x512=53.2ms。图5所示为主机写片外FLASH时序图。

3.2 读取数据并加载到片内DPRAM的时间

通过SO管脚读取AT25F1024的过程按下面顺序执行,当片选拉低选择此器件之后,通过SI线发送读指令,后面跟随要读的地址(三个字节地址),指令传输完之后,SI线上的任何数据将被忽略。指定地址的数据接着被移出到SO线上。如果仅读取一个字节,当数据读出来之后,CS信号驱动为高。读指令继续时,字节地址自动增加,并且数据不断被搬运出来。

AT25F1024缓冲数据寄存器大小2048位,在本设计中,写使能需要32个串行时钟周期,这样读取一次需要时间为2080个时钟周期,将片内DPRAM(DPRAM大小14940字节)填满,时间大约为2080x50ns(串行时钟40/2MHZ)x59(填满片内DPRAM需要大约59次读操作)=6.13ms。

4 结束语

本文从应用的实际需求出发,在FPGA中实现了对外部FLASH进行读写的高速SPI接口,并已在某型板卡中成功应用。本文重点用有限状态机的形式对各部分的工作原理和实现方法进行了描述。在FPGA资源比较紧张,限制管脚的使用数目,对速率又有比较高的需求的情况下,利用此SPI接口进行数据的加载或者固化,具有很高的应用价值。

- 基于Proteus的SPI接口的设计与实现(07-03)

- iEthernet W5200数据手册(版本1.2.4)之:外部接口(09-18)

- 车载MP3中Flash文件系统的设计与应用(11-11)

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- ARM硬件设计一:电源和时钟 (02-27)

- 大容量NOR Flash与8位单片机的接口设计(08-03)