基于ADSP-TS201S的多DSP并行系统设计

在宽带雷达信号处理中,存在诸如回波采样率高、脉冲压缩(匹配滤波)运算量大、处理流程复杂、实时高分辨目标检测困难等一系列问题。针对这些问题,采用通 用计算机平台难以应对运算量大和实时性等高要求,因此,需采用专用的数字信号处理器(DSP)来进行高速运算。尽管当前的数字信号处理器已达到较高水平, 但单片DSP芯片的处理能力还是不能满足宽带雷达的性能要求,需要引入并行处理技术,在本设计中使用4片DSP芯片组成并行处理系统。另外,为充分发挥 DSP芯片在复杂算法处理上的优势及FPGA在大数据量的底层算法上的优势,设计了一种基于FPGA控制的多DSP并行处理系统。

1 系统设计

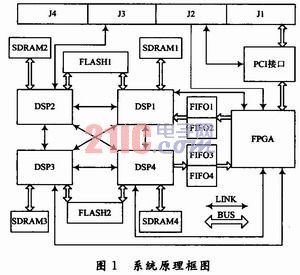

基于FPGA控制的多DSP并行处理系统的原理图如图1所示。

整个雷达信号处理系统以高可靠性CPCI工控机为平台,内置不同功能的信号处理板。板间的数据传输通过CPCI接口完成。根据雷达信号处理系统的任务分 配,本系统负责完成中频数字信号的处理。根据前端信号采集板输出数据的不同,数据将以串行或并行的方式输送到本系统中。其中,串行信号通过CPCI的J3 口以差分的形式直接传输给DSP2,然后在4片DSP芯片间按照预定的算法进行任务分配和并行处理,处理完毕后通过DSP4写入两片扩展连接成32输出方 式的FIFO中,此时,FPGA直接从FIFO中读取数据,完成与CPCI接口芯片PCI9656的时序转换后将数据发送到PCI9656,通过CPCI 总线经J1和J2口传输到雷达系统的其他功能模块。对于并行信号而言,32位带宽的信号首先通过J3口发送到F-PGA内部寄存器中FPGA接收到数据后 将数据写入输入缓存区,并在完成一帧后给并行DSP输出中断。当并行DSP采样到中断后,从数据缓存区读取数据,完成处理后,将数据传输到缓存 区,FPGA再通过相同的处理方式经CPCI接口的J1口和J2口将数据传输到雷达系统的其他功能模块。

2 DSP芯片选型

根据系统的性能要求,通过比较各种高性能DSP处理器,并着重对构成并行处理系统的性能和便捷性进行分析,确定选用AD公司的ADSP Tiger SHARC系列处理器中的TS201S组成多DSP并行系统。因为该系列的处理器在构成并行处理系统时其本身就提供了实现互连所需的片内总线仲裁控制和特有的链路口,可以以各种拓扑结构互连DSP,满足大运算量和片间通信灵活的要求。此外,选用ADSP Tiger SHARC还可以降低外围设计的复杂度,增强系统的稳定性。

TS201S芯片(600 MHz)主要性能指标:

(1)运行速度:1.67 ns指令周期;每周期可执行4条指令;

(2)DSP内部有2个运算模块,支持的运算类型有:32 b和40 b浮点运算;8 b,16 b,32 b以及64 b定点运算;

(3)每秒可执行12×109次16 b定点运算或3.6×109次浮点运算;

(4)采用单指令多数据(SIMD)模式,每秒可提供4.8×109次的40 b乘加运算;

(5)外部总线DMA传输速率1.2 GB/s(双向);

(6)4个链路口,每个链路口最高提供1.2 GB/s的传输速率,可同时进行DMA传输;

(7)多处理器处理能力,具有支持多处理器无缝连接的片内仲裁逻辑,多处理器采用统一寻址的方式访问,可以通过簇总线(ClusterBus)或链路口(Link Ports)方便地构成多处理器系统。

(8)片上SDRAM控制器,片上DMA控制器(提供14条DMA通道)。

3 DSP并行处理结构设计

ADSP-TS201S之间的数据传输通道可选择的方式有如下两种:高速链路口(LINK)方式和高速外部总线口(簇总线)。因此,由多ADSP- TS201 S组成的DSP并行处理系统从数据传输方式来看,不外乎有以下三种模型:高速链路口(LINK)耦合模型;高速外部总线口(簇总线)耦合模型;高速链路口 (LINK)与高速外部总线口(簇总线)混合耦合模型。

3.1 基于链路口的多DSP并行处理系统

在这种连接方式下,各DSP用LINK口连接在一起,进行通信控制和数据交换,系统结构简单、连线少、可扩展性强,在DSP具有多个 LINK口的情况下,可灵活组成线型、星型、环型、网络型或超立方体型等多种拓扑结构。ADSP-TS201S具有4个全双工的链路口通信端口。一个链路 口单向通信包含4位数据加上时钟与握手信号一共12条引线,双向共要24条引线。在内核时钟为600 MHz时,单向数据传输率最高可达600 MB/s,双向数据传输率可达1.2 GB/s,由于链路口通信是点对点的,所以具有很高的传输可靠性,但在传输数据时的共享性不如总线形式。

3.2 基于共享总线的多DSP并行处理系统

共享总线就是系统中所有DSP的外部总线(地址、数据和访问控制总线)都直接连接在一起,各DSP片内存储器和寄存器以及挂接在总线上的 外部存储器、外设都作为共享资源被各个DSP访问。ADSP-TS201S的外部总线为32 b,数据总线可以配置成32 b或者64 b。外部端口的运行速度最高可以到125 MHz,数据吞吐量可以高达1 GB/s。为了与不同外部设备连接,ADSP-TS201S外部端口支持快速(流水线)、慢速和SDRAM协议。且支持以DMA方式进行数据传输。另 外,ADSP-TS201S并行总线的最大特点是它具有无缝连接能力,无论是与SRAM、SDRAM、还是与处理器连接,只需要将相应管脚对应连接就能简 单方便的构成一个最多由8个DSP构成的多处理器系统,充分共享8个DSP的内部资源和外部的EPR-OM,SRAM,SDRAM等资源。

3.3 基于外部总线共享和链路口混合耦合的多DSP并行处理系统

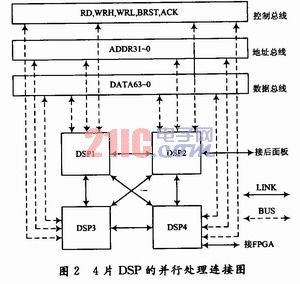

为兼顾数据速率、资源共享、易于控制以及DSP之间通信灵活等方面,在本设计中采用混合耦合模型的并行处理系统。将4个ADSP-TS201S的总线口都 相互连接好,各DSP的高速链路口也都相连,建立DSP到DSP的点对点通道与DSP间资源共享的工作块模式。4片SDRAM中,每两片扩展连接成64 位,挂接到64位数据总线上,2片FLASH也通过总线访问。控制总线连接到FPGA,由FPGA统一控制4片DSP之间以及DSP与外部存储器之间的数 据传输。4片DSP的工作块连接方式如图2所示。

- 一种基于FPGA的接口电路设计(11-18)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- 设计性能:物理综合与优化(04-28)

- 使用 PlanAhead Design 工具提高设计性能(04-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 面向 FPGA 的 ESL 工具(04-29)