基于自适应DVFS的SoC低功耗技术研究

时间:06-19

来源:作者:黄建科 周云

点击:

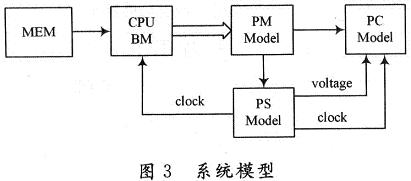

图3给出系统模型。构造这样一个系统,使得测试将按事先在开发板上的运行给定benchmark程序。测试得到的功耗参数,则按CPU负载折算成为归一的nop和mac两种类型指令程序,这两种指令在测试向量中间或分布。CPU行为模型执行相关程序,该模型只能取指令,执行2级流水。对于nop操作,在执行阶段进行nop;对于mac:操作,在执行阶段对固定数据进行mac,这样即可简化设计。CPU BM采用Verilog进行编写。CPU有一条AHB总线,对memory进行访问控制。MEM模块采用ahb接口,存放编译好的二进制指令,并固定频率。PM Model对CPU BM的翻转率进行monitotor在监控各阶段的翻转率后,作为输入流入自适应滤波器,计算得到所需的调节电压,给PS Model;同时输出翻转率,给PC Model。

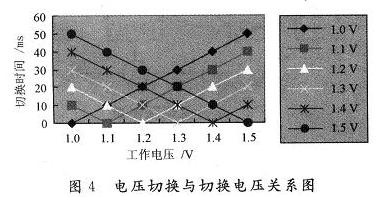

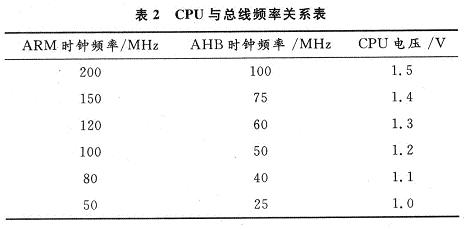

对于自适应选取的电压,可按图4予以实现。表2给出按照130 nm工艺实现电压时,CPU与总线频率的关系。在调节电压时,时钟被停顿若干时钟周期。假设电源网络的RC参数不变,则认为电压切换与切换电压差成正比,如图4所示。

4 结 语

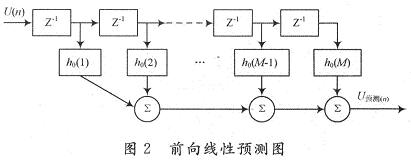

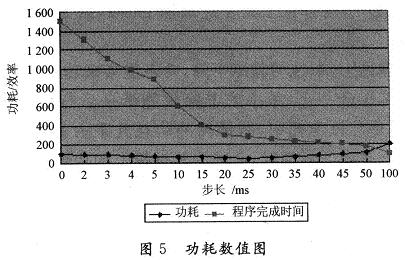

提供了一种自适应动态电压频率调节方式,构造了与之对应的系统模型。在计算机上对该模型进行了模拟实验,得到一组均衡的前向预测参数。实验结果验证了自适应动态电压频率调节方式的有效性,给出了评估动态电压频率调节仿真的有效途径。

- 高带宽嵌入式应用中SoC微控制器的新型总线设计 (02-02)

- SoC前段(ARM)嵌入式系统开发实作训练(上) (02-28)

- SoC前段(ARM)嵌入式系统开发实作训练(下)(02-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 开放源码硬件简史(05-21)

- 可配置处理器技术优势详解(05-15)