WTB网络HDLC在FPGA中的实现

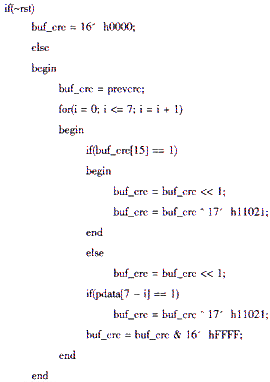

6+x12+x5+1进行计算,校验初始结果值应设为0xffff、图3中rst为复位信号,sig为事件触发电平,pdata为需要计算的数据,prevcrc为上一次计算的结果,crc最后输出的计算结果。Verilog核心代码为:

|

3.3 位同步

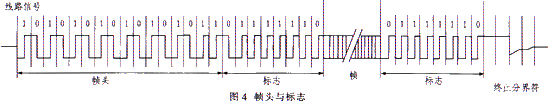

编码器发送有效帧序列,解码器对有效帧解析的最大难点在于起始的同步性。常用的同步方式有锁相环。但为了节省FPGA内部资源,针对WTB特有的帧头规则序列,采用高频采样比较方式进行同步。帧头在起始位和结束位"1"之间有7个("0","1")位对,如图4所示。在一个周期内,一位采样12次,若在位跳变的前后符合标准位,则同步开始,继续采样下一位,直到帧头位对全部完成,即使在空闲时,电平有干扰毛刺也不会产生误同步。

|

4 标准应用检验

通过使用Quartus II对WTB的编解码器的波形进行仿真,结果符合标准。

解码器在接收一个字节后进行CRC计算,当全部数据接收完成时计算出最后CRC结果;当全部CRC接收完毕接收到CRC结果,将这两种CRC结果进行比较。若数据合法则给一个脉冲。

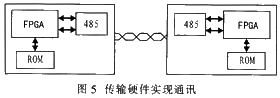

如图5所示,硬件采用485实现物理层与标准机车WTB网卡的通讯,能够相互解析,证明了设计的准确可靠性,为下一步应用层的设计打下基础。

|

5 结束语

针对WTB网络标准提出了一种基于FPGA的HDLC协议编解码器设计方案,并利用Altera公司的CYCLONE II EP2C8实现。目前对该网络协议的实现仅限于初期阶段,只能实现基本链路的HDLC数据编解码。该系统的后续还需加入NIOS进行链路控制的优化和应用层的设计,如WTB总线的初运行。实践表明,该编解码器实现简单、使用灵活,资源占用合理,对进一步工作的展开有深远意义。

- 三星ARM处理器S3C4510B的HDLC通道使用及编程 (05-03)

- 基于FPGA+ARM的HDLC协议控制器的设计与实现(06-29)

- 一种基于FPGA的接口电路设计(11-18)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- 设计性能:物理综合与优化(04-28)

- 使用 PlanAhead Design 工具提高设计性能(04-28)