基于U盘和单片机的FPGA配置

时间:08-25

来源:单片机及嵌入式系统应用

点击:

|

通常USB设备终端必须与计算机连接。如果没有PC,则需要通过USB总线的通用接口芯片(当然也可以利用带USB接口的单片机)控制U盘的读/写。本设计采用单片机AT89S52控制USB总线的通用接口芯片CH375来读取存储在U盘的配置数据。

CH375是一个USB总线的通用接口芯片,内部集成了PLL倍频器、主从USB接口SIE、数据缓冲区、被动并行接口、异步串行接口、命令解释器、控制传输的协议处理器和通用的固件程序等;支持USB-HOST主机方式和USB-DEVICE/SLAVE没备方式,可以方便地挂接到单片机/DSP/MCU/MPU等控制器的系统总线上。外部单片机可以直接以扇区为基本单位读/写常用的USB存储设备(包括USB硬盘、USB闪存盘和U盘)。

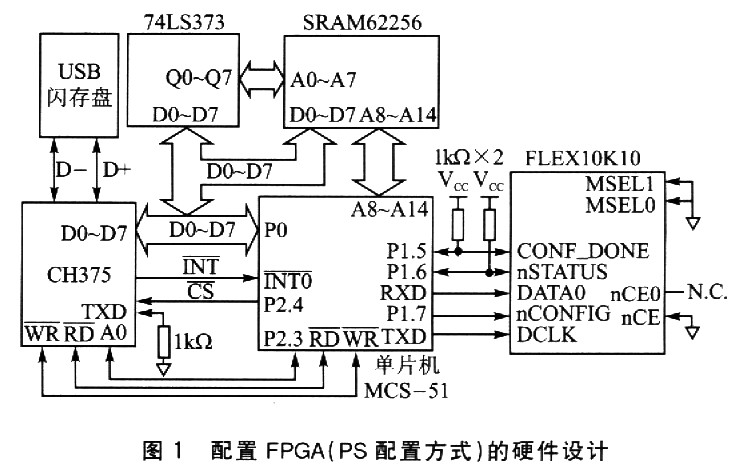

硬件设计:CH375工作于并口方式,与普通的MCS-5l单片机的连接如图1所示。CH375的TXD引脚通过l kΩ左右的下拉电阻接地或者直接接地,从而使CH375工作于并口方式。

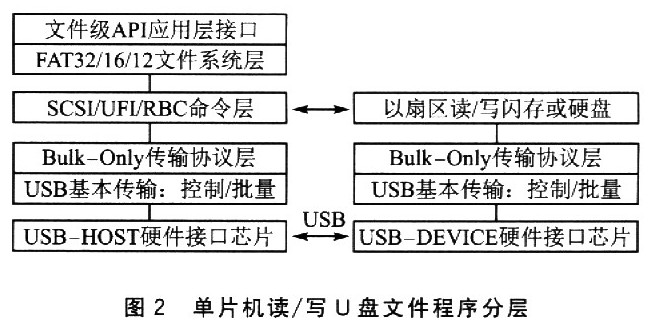

软件设计:①进入USB主机模式,要读/写U盘,必须先设置CH375使其工作于USB主机方式。②将U盘当作存储器进行读/写,方法与读/写闪存差不多,操作简单且速度快。单片机读/写U盘文件程序分层如图2所示。

|

FPGA器件上电以后,开始配置过程的复位、配置和初始化3个阶段,然后进入用户状态。以配置FLEX10K10为例,图3为PS模式下使用单片机配置FPGA的时序图。

|

|

FPGA器件的配置技术犹如集成电路制造中的流片,是非常重要的一个环节。用单片机配置FPGA器件与用专用器件相比,具有成本低、保密性好、可升级、可实现多任务电路结构重构(符合软件无线电思想)等特点,本设计具有创新性,硬件设计简单可靠,且成本低,易于实现,是确保FPGA安全性和保密性的一种方法,在金融等关系到国家利益的场合具有重大实用价值。

- 一种基于FPGA的接口电路设计(11-18)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- 设计性能:物理综合与优化(04-28)

- 使用 PlanAhead Design 工具提高设计性能(04-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 面向 FPGA 的 ESL 工具(04-29)