基于双Nios II的红外图像实时Otsu局部递归分割算法设计

1 引言

利用红外成像传感器实现实时目标成像跟踪是精确制导武器的核心技术,图像中目标的分割效果尤其是有效地使目标从背景中分离出来是保证系统稳定跟踪的关键,Otsu分割算法因其简单有效在实时目标成像跟踪系统中得到了很广泛的应用,用这种聚类准则分割图象,当目标在图象中占有适当的比例时,分割结果比较好。然而对小目标图象却不能把目标从背景中分割出来,经常会把很多背景错分为目标,本文提出了利用改进的快速局部递归Otsu分割算法对图象分割。并且依靠并行Nios II|0">Nios II软核和硬件逻辑结合的速度优势对算法实时实现。

2 算法原理

Otsu方法(即大律方法)在获得图像灰度直方图的条件下,利用概率论的知识,通过计算最大类间方差而得到分割门限.在较为理想的"双峰"条件下,用Otsu准则能够得到较好的分割效果。Otsu算法步骤如下:

在冷背景(如天空)下的红外飞机图像中,飞机目标的灰度级比较高,而且目标区域的面积往往要比背景区域的面积小一些,当两者面积相差悬殊时,简单的一次Otsu分割会错误地将部分背景划分到目标区域Otsu,考虑到一次Otsu分割的结果图像可以分为两部

分:背景区域和(含有部分背景的)目标区域.由于只对目标区域感兴趣,把背景区域去掉并不会丢失目标信息.那么,可以对结果图像的(含有部分背景的)目标区域进行Otsu分割得到新的结果图像,接着,把新的结果图像中背景区域去掉,若目标区域还包含有部分背景,则再对(含有部分背景的)目标区域进行Otsu分割,依次递归下去,直到得到比较理想的分割图像为止.这种方法称为Otsu局部递归分割方法。

对红外图像数据流处理时,由于Otsu局部递归分割算法需要对图像进行多次迭代处理,而且对每场图像分割需要的迭代次数不同,所以很难保证分割的实时性,为此我们提出了利用Otsu准则对图象进行两次局部递归分割。即在第一次Otsu方法分割之后,将分割得到的亮像素再次利用Otsu分割准则计算得到新的分割阈值。实验表明,即使存在复杂的云层背景的情况下,经过两次迭代分割后,目标也较好地被分割出来。

3 双Nios II的实现方案

Nios II嵌入式处理器是Altera公司于2004年6月推出的第二代用于可编程逻辑器件的可配置的软核处理器,性能超过100 DMIPS。NioslI是基于哈佛结构的RISC通用嵌入式处理器软核,能与用户逻辑相结合,编程至Altera的FPGA中。处理器具有32位指令集,32位数据通道和可配置的指令以及数据缓冲。它特别为可编程逻辑进行了优化设计,也为可编程单芯片系统(SOPC)设计了一套综合解决方案。NioslI处理器系列包括三种内核:一种是高性能的内核(Nios II/f);一种是低成本内核(Nios II/e);一种是性能/成本折中的标准内核(Nios II/s),它是前两种的平衡。本系统采用高性能内核。Nios II处理器支持256个具有同定或可变时钟周期操作的定制指令;允许Nios II设计人员利用扩展CPU 指令集,通过提升那些对时间敏感的应用软件的运行速度,来提高系统性能。

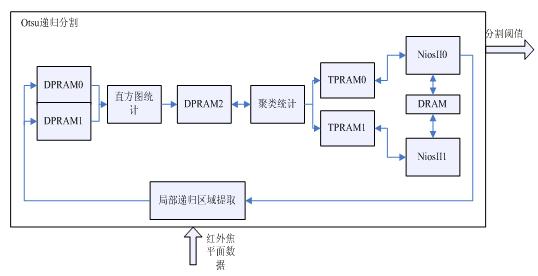

根据红外焦平面成像特性,为了保证算法的实时性,采用双Nios II软核和硬件加速器协同设计的方式,在图像场的间隙做实时Otsu局部递归分割处理。如图 1 所示实现算法原理图

图 1 算法实现原理图

局部递归区域提取单元将需要分割的红外数据读入FPGA内部双端口RAM0,直方图统计对数据统计直方图,存放于双端口RAM2,聚类统计单元分别对直方图依次从高低两个方向计算类内均值和概率,把累加结果存入三端口RAM0和RAM1中,聚类统计结束后,两个Nios II并行对高低两个方向的聚类统计结果进行类间方差计算并分别求最大值。取两者最大为分割阈值,完成一次分割后,局部递归区域提取单元依据得到的阈值提取出目标区域存入双端口RAM1中,接着按照第一次分割步骤完成快速局部0tsu递归分割算法。

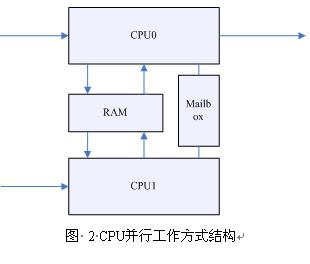

实现算法的CPU互联结构:

为了最大化的提高算法的处理速度,系统采用CPU并行工作方式。如图 2 所示,两个Nios II同时负责收发处理数据。当其中一个CPU执行完制定的任务后等待另一Nios II,当两个Nios II任务全部完成后,Nios II0从MailBox中取出Nios II1的处理结果计算最终分割阈值,采用这种将数据块分细处理结构,减少单个CPU处理的数据量,缩短了算法延迟。

考虑到算法需要进行循环的浮点数计算,采用Nios II的定制指令和VHDL编写硬件算法加速器保证系统运行速度,如图3 所示采用自定义浮点指令和软件实现浮点运算性能对比。定制指令逻辑和Nios II的连接在SoPC Builder 中

- 基于NiosII的SOPC多处理器系统设计方法(02-10)

- 基于NiosⅡ软核的嵌入式多路视频点播系统(04-23)

- 基于NiosII的二维条码识别系统设计(06-12)

- 基于IIS总线的嵌入式音频系统设计(01-29)

- 采用Virtex-5嵌入式三模以太网MAC进行设计(05-04)