基于NiosII的二维条码识别系统设计

时间:06-12

来源:

点击:

二维条码PDF417中PDF为Portable Data File的缩写,每一个PDF码的储存量可高达1 108字节,若将数字压缩则可存放2 729字节。作为一种新的信息存储和传递技术,PDF417具有成本低、信息可随载体移动、不依赖于数据库和计算机网络、保密防伪性能强等优点,广泛应用在国防、公共安全、交通运输、医疗保健、工业、商业、金融、海关及政府管理等领域,PDF417码的例子如图1所示。

1 系统总体设计

本系统在FPGA上使用SOPC技术来实现无线手持二维条码识读器,与传统一维条码识读器最大的区别在于完全脱离后台数据库,以及在高达50%破损率的情况下能够进行高效率识别。

1.1 系统硬件结构

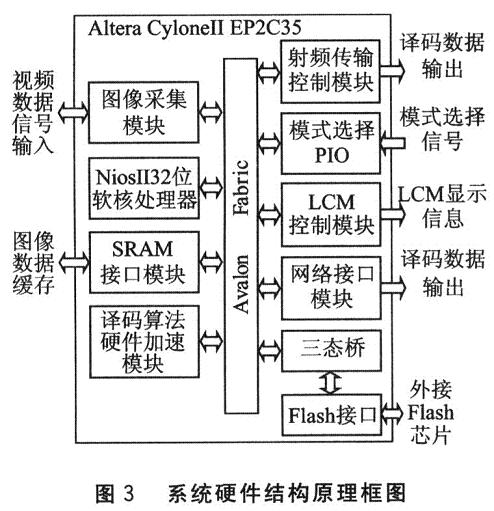

系统通过配置视频采集芯片ADV7181B,通过图像采集子系统将CCD采集到的条码数据存储在SRAM中后,产生硬件中断,处理器响应中断,Nios对SRAM中的数据进行图像预处理、译码及纠错,通过译码算法硬件加速模块对耗时较多部分算法进行优化,在实现条码数据译码及纠错后,产生射频传送和LCM显示中断,进入中断程序将译码数据通过射频传输模块发送到上位机,并且在LCM实时显示。其硬件平台结构原理如图3所示。

由于本设计采用的是灰度图,因此图像采集子系统的主要功能是:配置采集芯片,从解码芯片读出数据流,根据行场同步信号对数据流进行分离,提取出亮度信号,并将采集到的亮度信号通过乒乓缓存存入SRAM中。

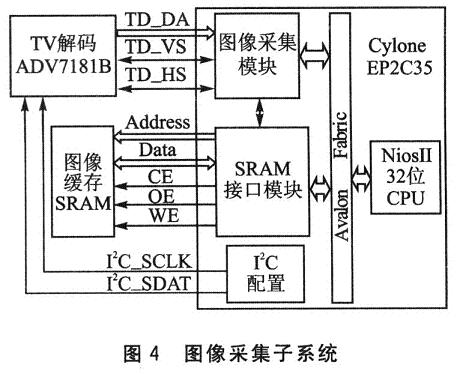

在设计中,采用ADI的解码芯片ADV7181B进行图像信号的数模转换,FPGA中的I2C模块是作为主设备来对ADV7181B进行配置的,而ADV7181B作为从设备来接受I2C总线传来的数据,实现芯片的初始化、寄存器的配置等。图4中T_DA为数据信号,TD_VS为场同步信号,TD_HS为行同步信号。

CCD摄像头采集的图像实际尺寸为768×576像素,每帧图像由奇场数据和偶场数据交错组合而成,奇场数据与偶场数据在时间上是先后输入的。本设计使用的是320×240的液晶显示屏,在处理过程中也采用的是320×240的图片格式,所以要对摄像头采集的图片进行提取。在设计中仅采奇场数据的中间240行,并对每行中间的640个数据每两个像素抽取一个像素,从而得到符合系统要求的图像大小。由于一帧图像的奇场数据与偶场数据实际上非常接近,而每行的相邻两个像素值也几乎没有差异,因此可以得到原输入图的缩小图像而不会有失真。

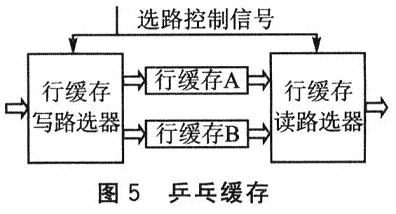

图像存入SRAM采用了乒乓缓存,如图5所示,是为了防止写出速度快于写入速度而导致出现错误数据。采用两个行缓存进行乒乓切换,在数据提取子模块向行A写入数据时,数据写出子模块读取行缓存B中的数据输出到总线;在对下一行进行采集时,对行缓存A读数据,对行缓存B写数据。因此行缓存写路选器与行缓存读路选器在同一时刻选通的一定是不同的行缓存。

条码译码主要流程是首先对条码进行自适应二值化,然后对条码进行定位、旋转、分割。分割出单个码字后,通过边缘检测,得到条码条空序列模块宽度后,再进行纠错解码。

传统条码识别算法在对条码定位时多采用Hough变换,通过Hough变换提取条码图像中的直线倾角来旋转条码。但是Hough变换的大运算量并不适用于实时性要求高的的嵌入式设备。笔者结合PDF417条码自身的特点,采用4点定位的方法来分割条码,有效提高条码识别速度。核心算法流程详细步骤如下:

(1)条码定位

实际采集条码时会出现各种倾斜,如图6所示。如何定位条码是关键的问题。可以利用条码起始头特有的比例来定位。按照国标的定义,PDF417二维条码的起始符黑白条空比是81111113,终止符黑白条空比是711311121。扫描图像的每一行,分别匹配起始符和终止符的条空比。考虑到条码采集过程中,边缘受高斯点扩展函数的影响,只要黑白条空比例的误差不超过三位,可近似认为符合比例。标记所有符合起始符条空比比例条码线段,可以得到4个控制点a、b、c、d,用同样的方法可以寻找符合终止符条空比的条码线段,确定点e、f、g、h。判断a、c、e、g是否为正确控制点的标准是,平行边长度误差在5个像素点内,且相邻边角度为90°,其误差角度为2°。

1 系统总体设计

本系统在FPGA上使用SOPC技术来实现无线手持二维条码识读器,与传统一维条码识读器最大的区别在于完全脱离后台数据库,以及在高达50%破损率的情况下能够进行高效率识别。

1.1 系统硬件结构

系统通过配置视频采集芯片ADV7181B,通过图像采集子系统将CCD采集到的条码数据存储在SRAM中后,产生硬件中断,处理器响应中断,Nios对SRAM中的数据进行图像预处理、译码及纠错,通过译码算法硬件加速模块对耗时较多部分算法进行优化,在实现条码数据译码及纠错后,产生射频传送和LCM显示中断,进入中断程序将译码数据通过射频传输模块发送到上位机,并且在LCM实时显示。其硬件平台结构原理如图3所示。

由于本设计采用的是灰度图,因此图像采集子系统的主要功能是:配置采集芯片,从解码芯片读出数据流,根据行场同步信号对数据流进行分离,提取出亮度信号,并将采集到的亮度信号通过乒乓缓存存入SRAM中。

在设计中,采用ADI的解码芯片ADV7181B进行图像信号的数模转换,FPGA中的I2C模块是作为主设备来对ADV7181B进行配置的,而ADV7181B作为从设备来接受I2C总线传来的数据,实现芯片的初始化、寄存器的配置等。图4中T_DA为数据信号,TD_VS为场同步信号,TD_HS为行同步信号。

CCD摄像头采集的图像实际尺寸为768×576像素,每帧图像由奇场数据和偶场数据交错组合而成,奇场数据与偶场数据在时间上是先后输入的。本设计使用的是320×240的液晶显示屏,在处理过程中也采用的是320×240的图片格式,所以要对摄像头采集的图片进行提取。在设计中仅采奇场数据的中间240行,并对每行中间的640个数据每两个像素抽取一个像素,从而得到符合系统要求的图像大小。由于一帧图像的奇场数据与偶场数据实际上非常接近,而每行的相邻两个像素值也几乎没有差异,因此可以得到原输入图的缩小图像而不会有失真。

图像存入SRAM采用了乒乓缓存,如图5所示,是为了防止写出速度快于写入速度而导致出现错误数据。采用两个行缓存进行乒乓切换,在数据提取子模块向行A写入数据时,数据写出子模块读取行缓存B中的数据输出到总线;在对下一行进行采集时,对行缓存A读数据,对行缓存B写数据。因此行缓存写路选器与行缓存读路选器在同一时刻选通的一定是不同的行缓存。

条码译码主要流程是首先对条码进行自适应二值化,然后对条码进行定位、旋转、分割。分割出单个码字后,通过边缘检测,得到条码条空序列模块宽度后,再进行纠错解码。

传统条码识别算法在对条码定位时多采用Hough变换,通过Hough变换提取条码图像中的直线倾角来旋转条码。但是Hough变换的大运算量并不适用于实时性要求高的的嵌入式设备。笔者结合PDF417条码自身的特点,采用4点定位的方法来分割条码,有效提高条码识别速度。核心算法流程详细步骤如下:

(1)条码定位

实际采集条码时会出现各种倾斜,如图6所示。如何定位条码是关键的问题。可以利用条码起始头特有的比例来定位。按照国标的定义,PDF417二维条码的起始符黑白条空比是81111113,终止符黑白条空比是711311121。扫描图像的每一行,分别匹配起始符和终止符的条空比。考虑到条码采集过程中,边缘受高斯点扩展函数的影响,只要黑白条空比例的误差不超过三位,可近似认为符合比例。标记所有符合起始符条空比比例条码线段,可以得到4个控制点a、b、c、d,用同样的方法可以寻找符合终止符条空比的条码线段,确定点e、f、g、h。判断a、c、e、g是否为正确控制点的标准是,平行边长度误差在5个像素点内,且相邻边角度为90°,其误差角度为2°。

- 基于NiosII的SOPC多处理器系统设计方法(02-10)

- 嵌入式网络地址监控系统研究与设计(08-01)

- 基于SBC+DSP的嵌入式系统设计与应用(08-02)

- 基于ATMEGAl28的语音识别系统的设计实现(07-09)

- 基于ATMEGAl28的语音识别系统设计(09-16)