基于ADSP-BF537的视频SOC验证方案设计

5总线转换状态机设计

目前,大多数采用AMBA总线的SoC系统内部的总线位宽是32位,多数嵌入式CPU和第三方IP核总线位宽也均为32位,因为32位地址总线和数据总线已经可以满足绝大多数SoC系统的存储器映射寄存器的地址分配和数据交换以及外部SDRAM和FLASH的寻址需求。ADSP-BF537的外部Memory数据总线是16位,并且地址总线只有19位,因此必须通过增加必要的状态来解决总线位宽的不匹配问题。

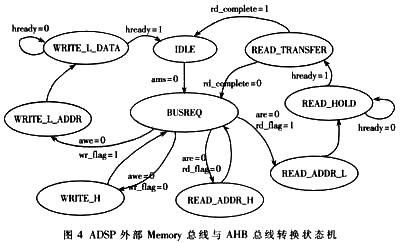

为了实现ADSP对外进行32位的地址操作和数据操作,可以利用Blackfin处理器分两次进行读写操作。写操作分两次进行,第一次写,先传输地址和数据的高16位,第二次写才将32位的地址和数据信号传输到AHB总线上;进行读操作时,需要AHB产生两次读动作,这样才能使有效的32位数据被Blackfin处理器正确接收。第一次读到有效的32位数据后传输高位,第二次读到后传输低位,并且每次读操作都需要Blackfin发出两次读动作,以便组合出AHB的32位地址。这样就可以突破ADSP-BF537对外只能进行4MB空间存取的限制。以上描述过程的状态机转换图如图4所示。

利用ADSP作为SoC系统处理器进行SoC验证时,ADSP进行的主要操作是读写系统内部各个功能模块的Memory映射控制寄存器,并且通过SDRAM控制器对SoC系统的外部SDRAM进行数据交换操作。因此总线转换状态机分成读传输和写传输两大部分。

当ADSP需要进行外部Memory总线传输时,首先会把相应的ams信号拉低,这时总线转换状态机应该使AHB进入BUSREQ状态,要求仲裁器释放AHB总线给CPU(ADSP)。

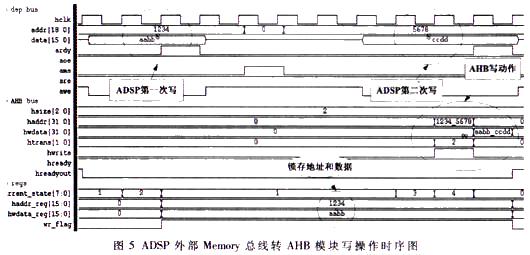

对于一个写操作,需定义一个wr_flag标志位来确定是否产生AHB写动作。ams信号拉低后,经过可配置的写建立时间后,写控制信号awe被拉低,初始化的wr_flag为0,表明ADSP进行的是第一次写操作。进入的WRITE_H状态用来锁存写地址和写数据的高16位,同时会把wr_flag置为1,但并不向AHB总线发出写命令。一个周期后重新进入BUSREQ状态,等待ADSP下一个写命令。ADSP发出第二次写命令后,状态机检测到awe=0和wr_flag=1后进入WRITE_L_ADDR状态,表明需要向AHB发出写命令,包括hwrite、haddr、htrans、hsize等AHB控制信号。haddr是两次写操作地址(16位)组合而成的32位地址,htrans=2和hsize=2,表明是非连续传输,传输数据位宽是32位。下一个周期,状态进入WRITE_L_DATA,两次写操作数据也相应组合成32位。如果AHB slave的hready为高,则32位数据释放到AHB总线上,同时复位AHB控制信号,下一个周期返回IDLE状态;如果hready为低,则继续保持WRITE_L_DATA状态,直到AHB slave把hready拉高有效。如果等待时间过长,可以增加一个计数器使状态机在一定时间后自动返回IDLE状态,并标记相应的error状态寄存器。例如,需要通过ADSP向haddr[31:0]=0x1234_5678地址内写入hwdata[31:0]=0xaabb_ccdd,则测试平台(采用vmt slave)模拟ADSP对外进行两次写操作,第一次向addr[18:0]=0x1234内写0xaabb,第二次向addr[18:0]=0x5678内写0xccdd,如图5所示。第二次写操作后正确产生AHB写操作。

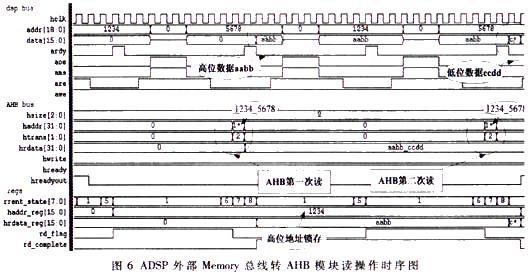

同样,对于一个读操作,状态机也需要两次对AHB发出读动作,把读到的slave数据分高低位两次传输给ADSP,不同的是,为了保证AHB读地址是32位,而不仅仅是ADSP外部Memory地址总线的19位,每次AHB的读命令,需要ADSP两次读动作,第一次读用来传输高位地址,第二次读才能把完整的32位地址传送到AHB上,使AHB产生读操作。上述过程的状态依次是图4中的READ_ADDR_H、READ_ADDR_L、READ_HOLD、READ_TRANSFER。标志位rd_complete用来区分AHB的两次读动作,为0时在READ_TRANSFER状态传输读取数据的高16位,被ADSP读取,下一个周期后进入BUSREQ状态等待下一个读命令;为1时在READ_TRANSTER状态传输读取数据的低16位,并返回IDLE状态。例如需要读取上述已经被写入地址haddr[31:0]=0x1235_5678的值时,第一次ADSP发出读addr[18:0]=0x1234,第二次发出读addr[18:0]=0x5678,这时ADSP的data只传输高位数据0xaabb,ADSP再发两次相同的读命令后,data才传输低位数据0xccdd。对应的读操作的仿真波形如图6所示。

如前所述,ADSP外部Memory总线在对外读写时可以通过EBIU_AMBCTlx寄存器来选择是否选通握手信号ARDY。为了提高传输的可靠性和准确度,在设计转换模块时需要考虑ARDY,如图5、图6中的读写操作时序图所示,在每一次数据传输完成的最后一个状态,需要将ARDY信号置1,然后在下一个IDLE或BUSREQ状态将ARDY清0,这样可以保证ADSP能正确读到ADSP外部Memory数据总线上的

ADSP-BF537 SoC FPGA Blackfin处理器 相关文章:

- 高带宽嵌入式应用中SoC微控制器的新型总线设计 (02-02)

- SoC前段(ARM)嵌入式系统开发实作训练(上) (02-28)

- SoC前段(ARM)嵌入式系统开发实作训练(下)(02-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 开放源码硬件简史(05-21)

- 可配置处理器技术优势详解(05-15)