模拟混合验证官 | Model的本质目标就是“时间+精度”

这篇文章,主要是Model的概览。做Model的本质目的是为了什么?想达到此目的的幕后推手是谁?做Model最核心的思想是什么;现在流行的 Model都有哪些种类,可以分成几个等级?和Model相关的、零散的、但是却很有用的概念有哪些?现有EDA工具中有哪些和Model相关的产品?且 听此文介绍。

如果去看大部分的介绍Model的书籍/Paper/培训教材,都会从目前是SOC时代、Model能大大提高仿真速度来作为背景介绍;我相信现在确实好多人都是在做SOC,SOC对于Model的需求远远大于纯Analog的。但是作为一名ADVer,一个以模拟出身的验证人,对于Model,我有自己更个性的看法。

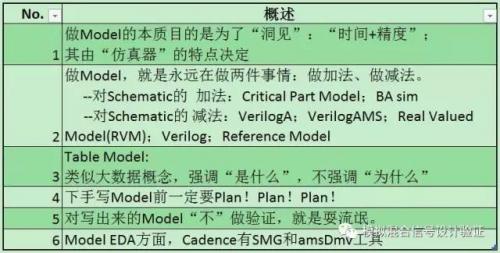

本篇文章主要是做Model的整体概述。首先介绍做Model的本质,继而介绍控制它的仿真器的特点,然后再介绍做Model的两个方向:做加法和做减法;然后重点详细讲解Model的等级。随后简单介绍一个"另类"的Table Model。然后强调做Model的战略性问题---Plan的重要性。另外简单介绍下做完Model要验证;在Model的产生和验证方面的现有Cadence工具。下表更直接点:其中前两个章节为本文重点章节。

了解完Model的整体概述之后,以后会陆续推出具体技术细节。例如做Model的基本功:各种语言的(主要是VerilogAMS)的写作技巧;做Model本身的技巧,注意事项,和Model的实例等等。

以下进入主题。

1. Model的本质目的

雷军雷布斯曾经说过"不要用战术上的勤奋掩盖战略上的懒惰"。做任何一件事情,搞清楚战略、想清楚目的,至关重要。那么问题来了,我们现在这里讨论做Model,那做Model的本质目的是什么呢?做Model的本质目的是为了"洞见"。所谓的洞见,就是明察,清楚的看到、而且提前看到,不要做马后炮的事情。"明察、清楚",这就是对"精度"的要求;"提前"就是对时间的要求。所以做Model这件事情的本质目标就是"时间+精度"。"时间、精度"是其永远逃脱不了的两个话题。

那问题又来了,"时间"和"精度",到底是谁在控制呢?显然是仿真器。所以搞清楚仿真器这玩意,才是基本功。就像我们高中回答所有政治题,只要有一句"生产力决定生产关系,生产关系反作用生产力",那么肯定能得分一样。金句,最底层的原理,其实很简单,搞清楚之后,通常事半功倍。

仿真器

在IC设计的EDA领域,最重要的仿真器,其实无非两种:数字Digital和模拟Analog,当然现在混合仿真器Mix-Signal也非常重要。他们是什么,之间有什么差别呢?仿真器其实也就是干两件事情,一个是时间,一个是数值。就是你在什么样的时间,会有什么样的数值(什么样的表现);只是对于数字和模拟,它是完全不同的处理原理,这主要是因为他们背后要解的方程组是完全不同的。

Digital仿真器

它是Event driven的,它解的是逻辑方程(logical expression),而且人家是顺序执行(sequential manner based),有很清晰的信号流和事件发生顺序(well-definedscheme of signal flow and events),不会回头计算,不做后悔的事情。所以它比较快,时间和数值都是离散的。也不容易出现不收敛性的问题。它甚至可以看完代码之后,大致先做个心中有数,知道有哪些Event要发生,然后等真正到达那个时间点附近时候,再看看有没有和其他事情抵消掉,抵消掉了,就不用发生了;抵消不掉了再发生(脑补一下我们小时候计算一些数学题合并同类项的感觉)。唯一的问题就是它只是和逻辑方程打交道,而现实世界、实际Transistor哪里是非黑即白的0,1世界,所以它的精度之类的天然的低;不过只要把各种协议和纠错功能做好,也倒是不影响它的出错。很多大的ASIC, SOC等,尤其是大规模集成的IC,都是Digital-On-Top,妥妥地必须用数字仿真器,快是它最重要的特性。

Analog仿真器

它须解决整个analog大环境、大矩阵( system matrix),而且是在每一个simulationstep,它都得站在全局观的角度,来看各种需求是否被满足。人家可是真正的信号与系统;所谓的信号,就是电压和电流;模拟仿真器都考虑。KCL,KVL,节点电流为0,回路电压为0,这都是让他们用简单逻辑方程理不清楚的事情。大大的矩阵必须建立起来才能Hold住好多的关系。任何一个analog里面的元素/器件(element)对其他原件都有直接影响(instantaneous influence);正所谓的"牵一发而动全身";当然也有不少EDA工具对较大的Analog电路做一下分割(Partition),以减小矩阵的规模。Analog仿真器每想往下走一步,都要先猜解一下,先给个结果的"小样"(类似我们平时买东西的送的小样儿),给了这个小样儿之后,再返回头看看是不是满足tolerance等各种大boss设置的种种条件门槛和要求;符合了,算是通过了一小步;如果没有符合,那再打回来、再改结果,再测试,再看看满足与否,直到最终通过各种要求;所以有时候这种迭代就把仿真器搞疯掉了,直接告诉你有convergence issue,我收敛不住了,罢工了,你看着办吧。

- 模拟混合验证官 | 谈模拟混合信号设计验证?先从这个职位说起吧!(03-02)

- 模拟混合验证官 | DV这个职位不是说服了老板就能招到人!(03-08)

- 模拟混合验证官︱Table Model是什么?可以和大数据联系起来(04-13)

- Maxim推出单节和2节电池电量计IC(06-14)

- 特斯拉:车是卖不动了,先卖电池吧(03-23)

- 特斯拉Model S车主喜大普奔:专属无线充电器近了(01-25)