T-Clock技术 实现PXI整合同步测试

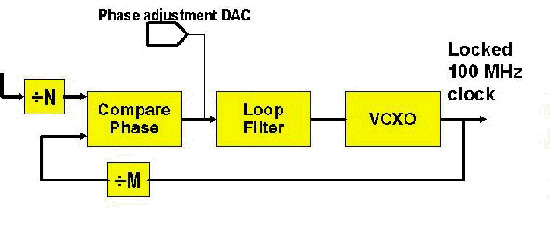

NI 的 PLL 设计中,有一项非常有用的特性,就是使用一颗相位 DAC。使用相位 DAC 时,可将"VCXO 输出"和"输入的参考频率"进行相位对正。表面上,VCXO 输出与参考频率同相;但可能必须将 VCXO 输出略为偏斜,使输出的相位稍微偏斜。当送进各设备中的参考频率因为传送延迟而有些许偏斜时,则该项功能对于校准多部设备的取样频率就非常重要。举例来说,在 NI PXI-1042 的机架中发送 10 MHz 参考频率时,插槽至插槽的偏斜最高有 250 ps,最多有 1 psrms 的抖动。虽然 250 ps 的插槽至插槽偏斜对大部份应用而言没有问题,但可能不适合极高速应用;因为其相位准确度很重要。为了解决这个偏斜问题,相位 DAC 的输出可加以调整,以校正偏斜。在 NI PXI-5422,200 MS/s取样率的任意波形发生器,与 NI PXI-5124,200 MS/s 取样率的示波器中,取样频率的相位/延迟调整为 5 ps,因此使用者在同步化多部设备时,可拥有极大的弹性。

图 8. 具备相位调整 DAC 的 PLL──相位 DAC 使取样频率对应于参考频率的延迟更加有弹性。

触发器偏斜与扭曲

在解决取样频率同步化的问题之后,另外一个主要问题就是发送触发器以启动同步作业。触发器可能来自1 个数字事件,或来自符合触发条件的模拟信号。一般来说,在多信道系统中,其中1 部设备被设定为主要设备,其余的则指定为从属设备。在这个情况下,主要设备将发送触发信号给系统的所有从属设备(包含其本身)。这里出现的2 个问题为触发延迟 (delay) 和偏斜 (skew)。从主要设备发送到所有从属设备时会发生触发延迟,而每部从属设备之间会发生扭曲;此现象虽无法避免,但是此种延迟与偏斜均可加以测量,并进行校正。

然而在测量延迟与偏斜时,所面对的挑战分成两个阶段:

1. 自动测量主要设备和每一部从属设备之间的触发延迟,并进行补偿。

2. 确保从属设备之间的偏斜极小,以确保所有设备皆在同样的频率范围内收到触发器。

将触发信号发送到多部设备,需要将触发信号传送到取样频率的频率范围中,使触发器能在正确的时间点上传送到每一部设备。

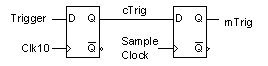

在取样频率低于或等于 100 MS/s 时,偏斜会成为触发器正确发送的主要障碍。举例来说,若系统内含10 部 200 MS/s 取样率的设备,每部设备必须在 5ns 的时间范围内收到触发。则此限制对于想要提供 100 MHz 以上频率与同步的平台造成明显负担。触发信号必须以低于取样频率的频率范围发送,否则必须建立1 个未经总线的方式来发送触发器信号(如点对点联机)。这种平台的价格过高,并非使用主流。因此必须采用另外一个发送通道:让触发器信号使用低频率范围,以稳定地发送,并且传送到高速取样频率范围。理想的选择之一,即为同步化触发器信号的发送与 10 MHz 的参考频率。但是,当取样频率并非10 MHz 参考频率的整倍数时,就无法确保2 组适配卡能于同一个取样频率周期中收到触发器信号。为了说明这一点,假设2 部设备拥有图 9 所示之简单回路4,供触发器从 10 MHz 参考频率范围传送到取样频率范围。

图 9. 10 MHz 触发器自参考频率范围传送至取样频率范围

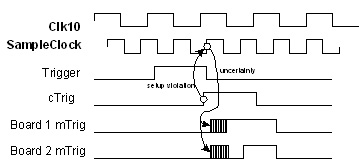

即使设备的取样频率相同,以下的频率图表显示在2 部装置中,无法于相同取样频率周期中看到触发的原因。

图 10. 亚稳定 (Metastability) 在触发器上的效果

第一次触发器的输出(cTrig) 可能发生在过于接近取样频率升高边缘的地方,导致mTrig 变成亚稳定(metastable) 状态。当稳定状态安定下来时,在不同的设备上可能有不同的处理方式,导致将同一个触发器信号视为发生在不同时间的2 个事件。

八、SMC 模块仪器与 TClk

2003 年时,NI 以同步化与内存核心(Synchronization and Memory Core,SMC) 为基础,推出第一代PXI 示波器、任意波形发生器,与数字信号发生器/分析仪。SMC 中使用的关键技术之一,就是供频率与同步应用的T-Clock (TClk) 技术。

TClk

NI 开发1 种同步化的方法,当布署另外的信号频率范围时,可启用取样频率校准,与触发的发送和接收。Tclk 技术的目标包含2 方面:

• TClk 可针对已相位锁定10 MHz 参考频率,但却未校准的取样频率进行校准。

• TClk 可正确触发同步化后的设备。

TClk 同步化即具弹性,而且范围广阔;可应用于下列环境中:

• 使用NI PXI-6653 Slot 2 系统频率与控制模块,从单一PXI 机架延伸至多部PXI 机架的同步化,以配合大型通道之用。

• 同质予异质同步化──使用外部或内部取样频率,以相同或不同取样率运作的设备。

• TClk 同步化可以运用在模式一与模式二中,如上文所描述。

- 使用PXI测试平台测试下一代无线设备(03-19)