T-Clock技术 实现PXI整合同步测试

NI 4472 与NI 4461,分别为24 位104 kS/s 与208 kS/s) 即使用这种技术进行同步化,应用于声音与振动测量。

这种模式是最单纯的相位连贯取样模式;多部设备接收相同的取样频率。因此所有设备都获得相同的取样频率正确性、偏移,与抖动。这种模式的缺点在于无法满足所有相位连贯同质频率的需求。

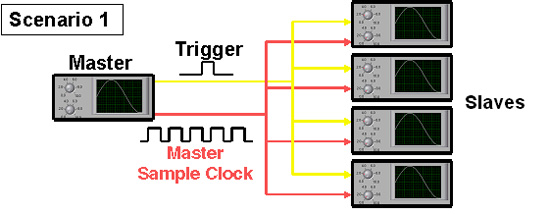

图 3. 使用取样频率进行同步化

五、同步化模式之二:使用参考频率进行同步化

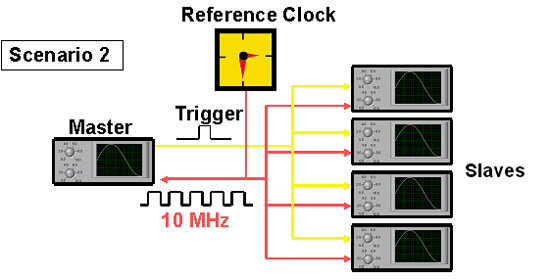

亦可在多部测量设备之间使用相同触发器与参考频率,以达成同步化。在这种模式中,参考频率可以由主要设备提供(主要设备必须内建参考频率),或是由专用的高精度频率来源提供参考频率。

这种模式的优点,即可从单一参考频率取得同样的取样频率,让所有的取样频率皆锁定于此相位。缺点是各设备上的相位连贯取样,并不如直接使用取样频率那样单纯,因为每一部设备的时间都会产生影响,因此必须考虑到设备频率的抖动问题。

PLL 即经常采用此种模式进行同步化,并产生取样频率。

图 4. 使用参考频率进行同步化

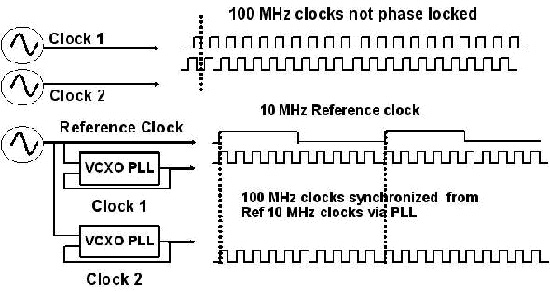

图 5. 高速的取样频率使用 PLL 进行同步化。

六、同步化的问题

发送频率与触发器以获得高速同步化之设备,遭遇到些许的问题。针对同步化而言,必须协调多部测量设备的潜在因素与时间不确定性;对于高速测量系统而言更是如此。工程师往往在最初的系统设计时间中忽视这些问题,而限制同步化系统的速度与准确性。在发送频率与触发器时的2 个主要问题,即为偏斜(skew) 与抖动(jitter)。

七、取样频率同步化

以本质来说,混合信号测试需要在各仪器上采用不同的取样率,因为模拟波形 I/O 与数字波形 I/O 必须采用不同的取样率;但是均必须进行同步化。更重要的一点,必须在各仪器上,以正确的取样频率边缘进行数据取样。

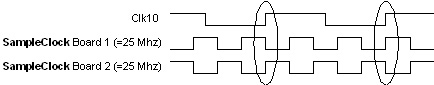

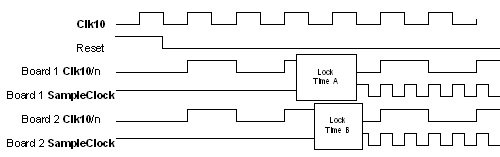

当不同仪器上的取样频率均为 10 MHz 参考频率的整倍数时,所有的仪器都将拥有与其他仪器同步的取样频率──所有取样频率的提高间距都与 10 MHz 频率边缘 (edge) 相符。如图 6 所示,尽管已锁定相位为 10 MHz 参考频率,但当取样频率不为整倍数时(如 25 MHz),就不能保证取样频率同相 (in phase)。目前使用标准技术来解决这个问题,即同时重新设定所有的 PLL,使得同频率的取样频率变成同相,如图 7 所示。即使此时所有的取样频率皆为同相,但是此解决方法仍然不完全。完全同步化为:从设备到设备的数据时间,位于一个取样频率周期中。完全同步化的关键在于触发,将于下文中讨论。

图 6. 未校准之 25 MHz 取样频率

图 7:使用重设使 PLL 同步化

频率偏斜(skew) 与抖动(jitter)

工程师必须仔细规划取样频率与/或参考频率的发送。举例来说,一个经同步化的测量系统若要以 200 MS/s 取样率,于 20 个通道同时进行取样。则表示要将频率发送到 10 个双通道的示波器。如果取样频率偏斜 1%,则偏斜不能大于 25 ps。这样一个系统看起来极具挑战性。还好,偏斜限制可针对每部测量装备的偏斜进行校正来解决;可以在取样数据中,就偏斜部份加以补偿。真正的问题是频率频率。无论是发送一个 200 MHz 直接取样频率或 10 MHz 参考频率,都会在系统中造成抖动。发送系统的物理性质,在发送频率的准确性上扮演重要角色;如果频率的路径容易受到高频电子噪音的影响,那么频率抖动就会成为明显的问题。针对用于发送高频取样频率的平台,制造、测试,与校正都变得极为昂贵。因此在许多高频系统中,普遍会使用较低频的参考频率来进行校正。图 8 是安装在NI SMC 模块仪器中的典型 VCXO PLL。回路带宽维持在最低,以防止来自参考频率的抖动,同时设备 VCXO 的抖动则低于 1 psrms。这样的系统可以有效地成为一个低抖动的同步系统。

NI 的 PLL 设计中,有一项非常有用的特性,就是使用一颗相位 DAC。使用相位 DAC 时,可将"VCXO 输出"和"输入的参考频率"进行相位对正。表面上,VCXO 输出与参考频率同相;但可能必须将 VCXO 输出略为偏斜,使输出的相位稍微偏斜。当送进各设备中的参考频率因为传送延迟而有些许偏斜时,则该项功能对于校准多部设备的取样频率就非常重要。举例来说,在 NI PXI-1042 的机架中发送 10 MHz 参考频率时,插槽至插槽的偏斜最高有 250 ps,最多有 1 psrms 的抖动。虽然 250 ps 的插槽至插槽偏斜对大部份应用而言没有问题,但可能不适合极高速应用;因为其相位准确度很重要。为了解决这个偏斜问题,相位 DAC 的输出可加以调整,以校正偏斜。在 NI PXI-5422,200 MS/s取样率的任意波形发生器,与 NI PXI-5124,200 MS/s 取样率的示波器中,取样频率的相位/延迟调整为

- 使用PXI测试平台测试下一代无线设备(03-19)