接地和去耦:现在就开始学习基础知识,为日后铺平道路!第三部分:去耦续篇

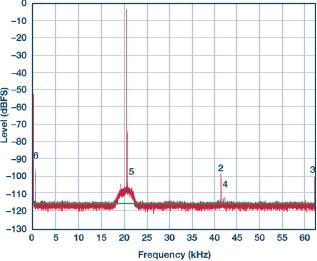

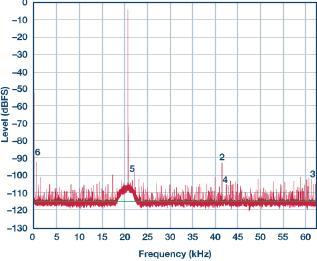

图4:正确去耦时AD9445评估板的FFT图

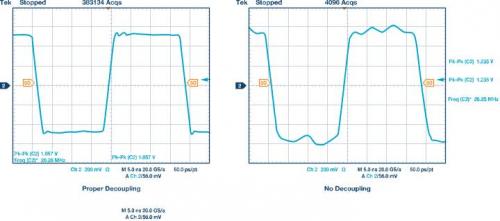

图3.去耦对AD8000运算放大器性能的影响

P03

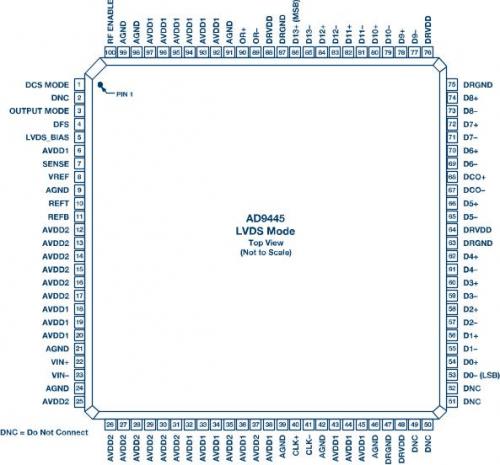

AD9445的引脚排列如图4所示。请注意,电源和接地引脚有多个。这是为了降低电源阻抗(并联引脚)。

模拟电源引脚有33个。18个引脚连接到AVDD1(电压为3.3 V ± 5%),15个引脚连接到AVDD2(电压为5 V ± 5%)。DVDD(电压为5 V ± 5%)引脚有4个。在本实验所用的评估板上,每个引脚有0.1 μF陶瓷去耦电容。此外,沿电源走线还有数个10 μF电解电容。

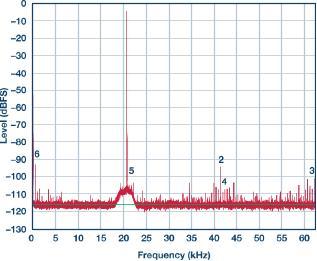

图6显示了从模拟电源去除去耦电容后的频谱。请注意,高频杂散信号增加了,还出现了一些交调产物(低频成分)。信号SNR已显著降低。本图与上图的唯一差异是去除了去耦电容。

图6.从模拟电源去除去耦电容后AD9445评估板的FFT图

图5.AD9445引脚排列图,来自图4 AD9445数据手册

P04

图7显示从数字电源去除去耦电容的结果。注意杂散同样增加了。另外应注意杂散的频率分布。这些杂散不仅出现在高频下,而且跨越整个频谱。本实验使用转换器的LVDS版本进行。可以想象,CMOS版本会更糟糕,因为LVDS的噪声低于饱和CMOS逻辑。

图7.从数字电源去除去耦电容后AD9445评估板的SNR图

这些实验表明,除去大多数或所有去耦电容会导致性能降低,但要分析或预测除去一两个去耦电容的影响是很困难的。当拿不定主意时,最佳策略是放上电容。虽然成本略有增加,但消除了性能降低的风险,这样做通常是值得的。

去耦总结

关于去耦的内容还有很多,但我们希望大家对其在实现系统期望性能方面所起的作用有了一个大致了解。这些文章中的基本纲要说明了关键概念,欲了解详细信息,请参阅其他参考资料。另一个宝贵的指导资源是制造商的评估板,大部分IC产品都有相应的评估板。很多情况下,您只需下载原理图、布局和元件列表,然后了解关于去耦做了些什么,而不必实际购买评估板。您可以确信,这些评估板的设计非常用心,旨在实现待评估IC的最佳性能。

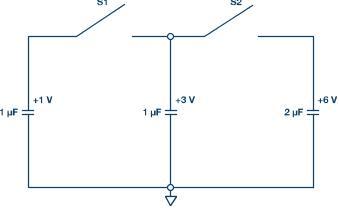

现在我们用图8所示的传统电路测验结束本文。

图8.测验:三个理想电容充电到所示电压。先闭合S1,再闭合S2之后,该组电容的最终电压是多少?如果开关闭合的先后顺序相反,该组电容的最终电压是多少?

- 正负电源基础知识以及如何符合双向可控硅触发要求(10-07)