TPIC46LO1 串行模式控制

时间:10-02

整理:3721RD

点击:

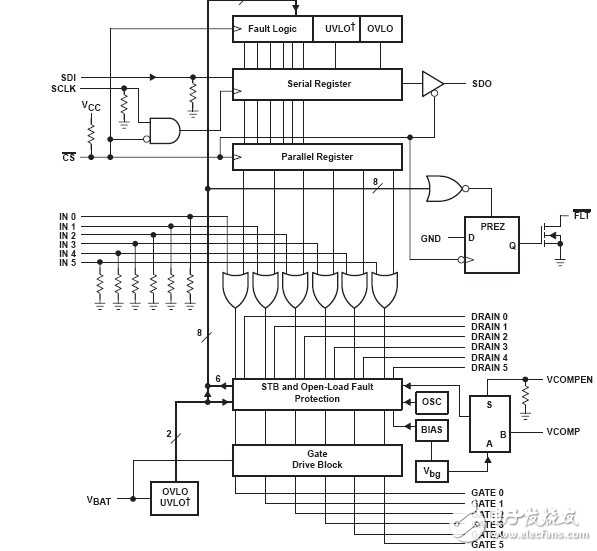

各位大神,谁用过这个芯片吗?串行模式下,IN0-IN5接地,通过SDI串行输入控制GATE0-GATE5段的FET。应该怎样实现呢?另外,DRAIN0-DRAIN5应该怎样处理?[img]file:///C:\Users\dell\AppData\Roaming\Tencent\Users\980246838\QQ\WinTemp\RichOle\82XD[4{N3L]SFI{XQ[I7T]F.jpg[/img]

TPIC46LO1串行模式控制

芯片时钟SCLK频率,最大10MHz,

CS 设置为低电平

SOI 8bit, 分别是OV,UV,FLT5 到 FLT0,FLT是FET控制信号,低电平关,高电平开

DRAIN0-DRAIN5是信号输入端,Gate0-5是信号输出端,In0-5用于parallel模式

更正一下,我的意思是Gate0-5是控制信号输出端,可以当作普通的I/O端口使用