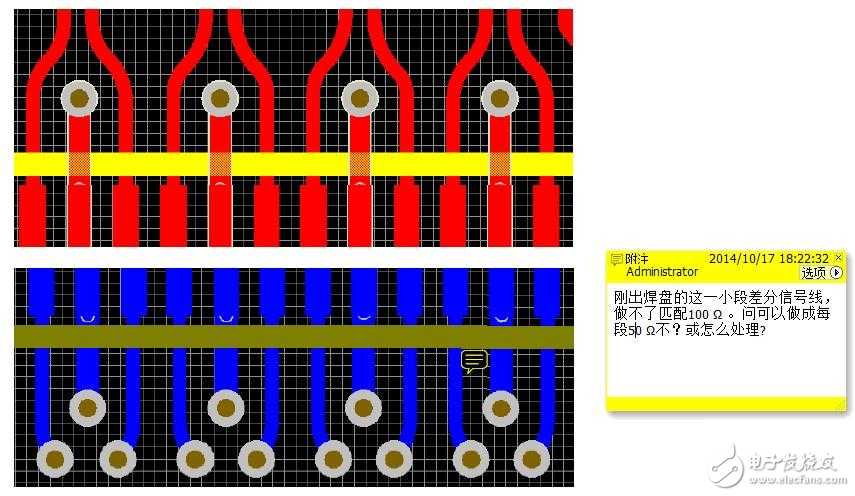

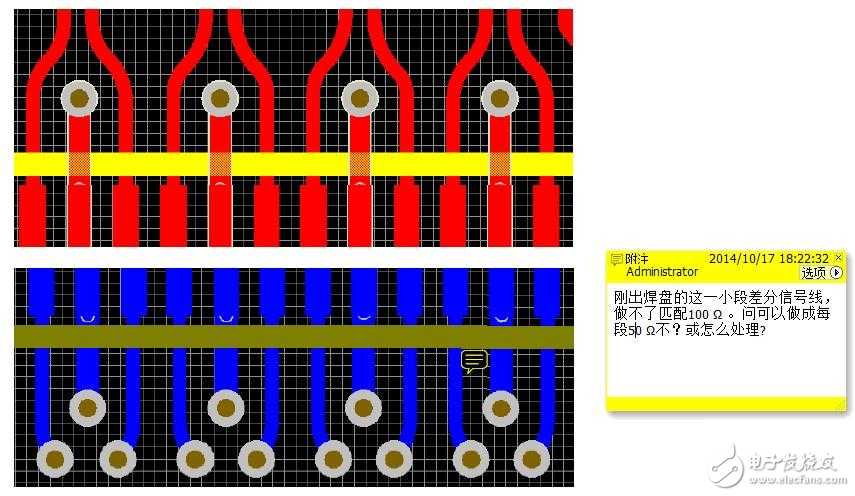

刚出PIN的一小段差分信号线满足不了100 Ω,该怎么处理?

时间:10-02

整理:3721RD

点击:

阻抗匹配问题像这些刚出PIN的一小段差分信号线满足不了100 Ω,该怎么处理?可以作成每根(就这一小段)50Ω不?在满足差分100欧后,这一小段做单端做50欧就很难设计了,这该怎么处理呢?

求大神指点,谢谢!

求大神指点,谢谢!

这种很正常啊,像引脚间距稍远,BGA底下线宽过小这种是最常见的。- v7 m# b- u, O

这种情况下,我们没法坐到严格一致,我们只能尽量保证不连续的走线越短约好,因为我们最简化考虑的话,假如这根不连续的线有1mm长,那么信号传递到这里时,先有一个上冲,那么么恢复阻抗时候就又有一个下冲,假如你信号是100M,那么对于这1mm的线长,传输延迟完全可以忽略,这两个上下冲,就可以视为刚好完美叠加,那就基本可以忽略起影响。

BGA底下这种百兆级的信号线是可以这样处理的,但这每对差分的速度有6Gbps啊,这样不行吧?

对于这种五六G以上的 肯定要特殊处理,想办法保证了,不过也不是绝对的,有时候还是退而求其次,一点点的阻抗变化,还是可以接受的。4

对于这种五六G以上的 肯定要特殊处理,想办法保证了,不过也不是绝对的,有时候还是退而求其次,一点点的阻抗变化,还是可以接受的。4

那一小段可以不控阻抗,没关系!(这四对是视频信号?)

恩,是HDMI 2.0的那四对TMDS信号,传输音视频的信号,每对差分的速度有6Gbps啊,这样不行吧?

那你那个地孔可以打在另外一端不。如果可以的话,应该可以保证差对的阻抗。如果不 行的话,也只那样了吧!

可以出来后靠近芯片串各电阻,假如出来那一小段是50Ω,再串一个50Ω的。