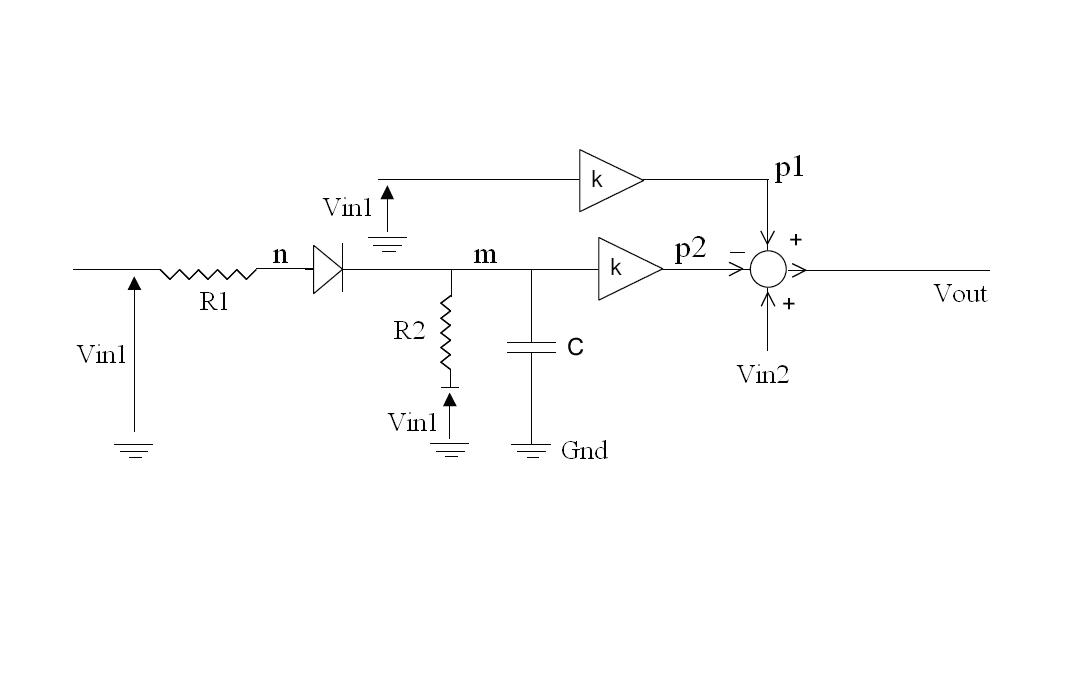

How to realize the subcircuit, plz help!

1、I’m confused that the condiction diode is working, how to describe the behavior of the diode.

Vn>Vm, then the diode is open; Vn<Vm, then the diode is closed. Or, Vin1 is increased, the diode is open; Vin1 is decreased, the diode is closed. How to realize the diode in ADS?

2、The other problem is that

Vout=Vp1+Vin2-Vp2, how to realized these in ADS, is there any term in the palette can fulfill the function.

The subcircuit can also be realized in verilog-A, but I have no idea about that.

Does anyone can give some constructive advices about the problem!

thank you all!

pursue

If you want to substitute diode as ideal voltage switch, use following.

http://edocs.soco.agilent.com/displa...lled+Switch%29

If you want to use physical diode modeling, there is an example written by SDD(Symbolically Defined Devices).

See "Full Model Diode, with Capacitance and Resistance" in the following.

http://edocs.soco.agilent.com/displa...efined+Devices

BTW why don't you use builtin diode of ADS ?

http://edocs.soco.agilent.com/displa...ction+Diode%29

You can use this diode with default model parameter sets.

Use following.

http://edocs.soco.agilent.com/displa...tage+Summer%29

http://edocs.soco.agilent.com/displa...tage+Source%29

or

http://edocs.soco.agilent.com/displa...nd+14+Ports%29

If you want to bulid Verilog-A block, see the following.

http://edocs.soco.agilent.com/displa...+Design+System

In the following, you can see an example of diode description using Verilog-A.

http://edocs.soco.agilent.com/displa...t+in+Verilog-A

However native behavioral modeling in ADS is SDD(Symbolically Defined Devices) not Verilog-A.

http://edocs.soco.agilent.com/displa...efined+Devices

http://edocs.soco.agilent.com/displa...nd+14+Ports%29

If you don't use your blocks in other simulators, you don't have to describe your blocks as Verilog-A.

System Model such as SwitchV and VSum require license.

Also Verilog-A require license.

If you build all blocks by SDD without using System Model and Verilog-A, no additional license is required.

realize subcircuit plz 相关文章:

- How to realize inductor from transmission line (micro-strip and CPW lines)

- Measured realized gain pattern values

- How to plot phase of realized gain of antenna pattern in HFSS like CST Software

- How to realize Short-Open-Load-Thru(SOLT) de-embedding procedure manually in ADS?

- How to realize a parallel RC circuit given the real and imaginary part of impedence

- Could LED array realize light's beam forming like antenna 's beam-forming?