fractioan frequency synthesis ( FSK transmitter )

1 f1;

0 f2;

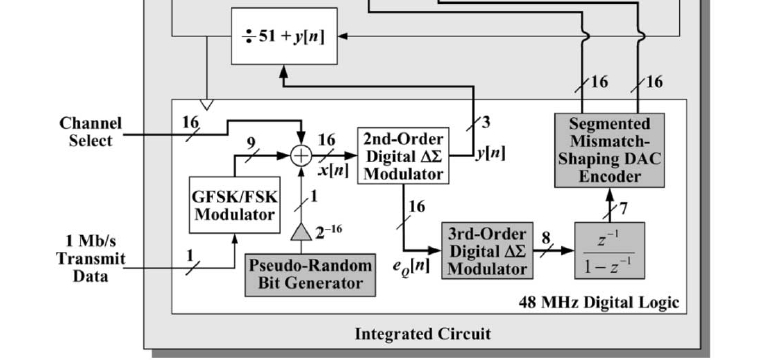

but in a JSSC paper(2004), the transmit data changes from 1 bits to 9 bits after a FSK modulator ( In the follow picture).

Can anybody tell me the reason?

Diagram looks like part of dual port modulator.

For FSK on a synthesizer you need to modulate the reference clock dividers and main VCO dividers so the effective phase difference at synthesizer phase detector is cancelled. This prevents the synthesizer loop from washing out the FSK modulation.

Fractional-N synthesizers just dithers the dividers at a high rate, many times the loop bandwidth to get effectively fractional divide ratios.

Old analog modulation injection applied FSK modulation to reference crystal and to VCO in the correct ratio. (ratio reference to VCO modulation changes with synthesizer channel setting since VCO divide N is changing with channel). Modern techiques use DSP digital translation of FSK to directly create the modulation with its slew rate shaping by rapidly changing the divider settings to the Frac-N synthesizer to create the FSK.