模拟电路为什么那么难?

时间:10-02

整理:3721RD

点击:

多多指教。

好久不见!

持续关注,表示改成走线电源后效果如何?

基本解决

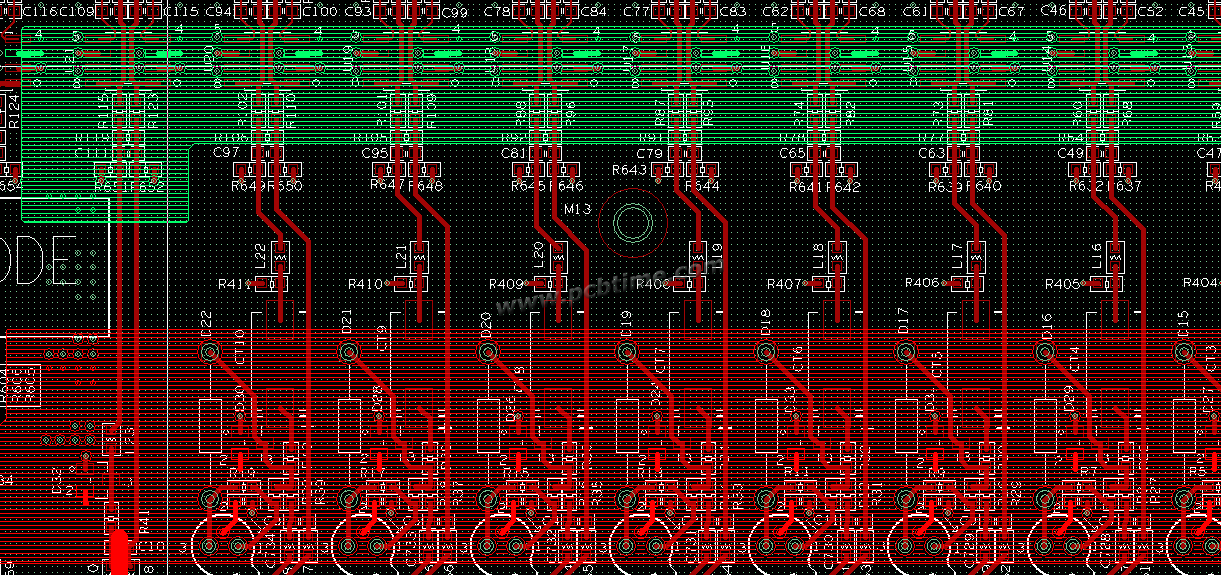

修改前: 1 正负12V 铜皮处理(绿色,一个在负片),24V铜皮处理(红色) 2 由于硬件定义原因,gnd(l绿色)无法和pgnd(红色)无法完全隔离,虽然同层已做较大距离避让, 无法确认是高压电源引入的问题,还是pgnd引入的问题,导致芯片易损坏

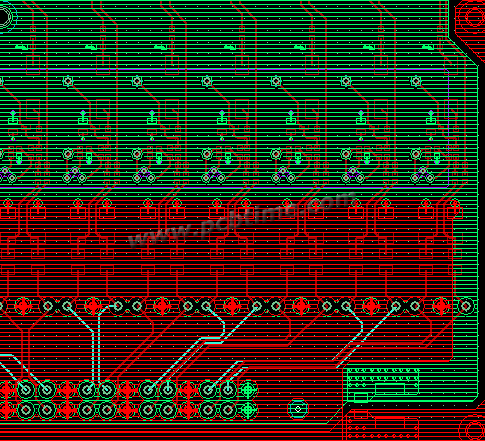

修改后:

1 电源粗线处理

2 pgnd通过改原理图,基本实现完全隔离gnd

结果:

修改后,客户目前暂未发现芯片损坏,当然还需要长期时间的验证,但初步来看,这种没太大的问题,对于模拟电路,在保证电流的情况下,最好能布线或者窄铜皮处理,避免带来的干扰,忌采用数字电路的大面积铺铜方法,忌无关电源铺入。

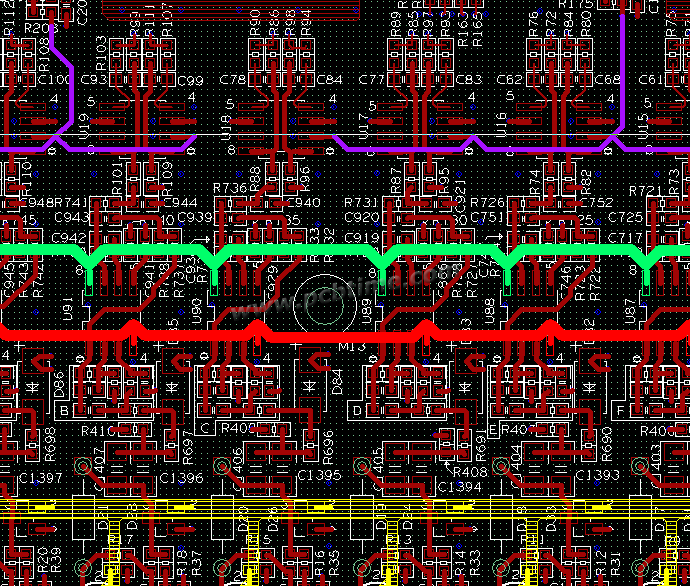

我们设计不都是数模隔离吗(包括数字电源和模拟电源)、24V走线与5V/12V模拟交叉当然风险很大,我觉得一部分是布局的原因、一部分是结构或者功能模块的划分、然后就是原理图的合理性。我们设计的时候一般24V输入电源都会原理数字模块和模拟模块,然后将电源的树状分布合理化

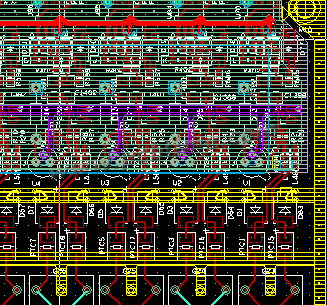

上个图片,典型的数模分离和电源配置方案

24V没有和12V交叉,是模拟本身的12V电源。而且24V也是模拟部分保护的电源,本身数模部分都已经彻底分开了。模拟部分自身的高压电源,布局基本上无法分开.