高速差分之间的间距是否需要均匀?

时间:10-02

整理:3721RD

点击:

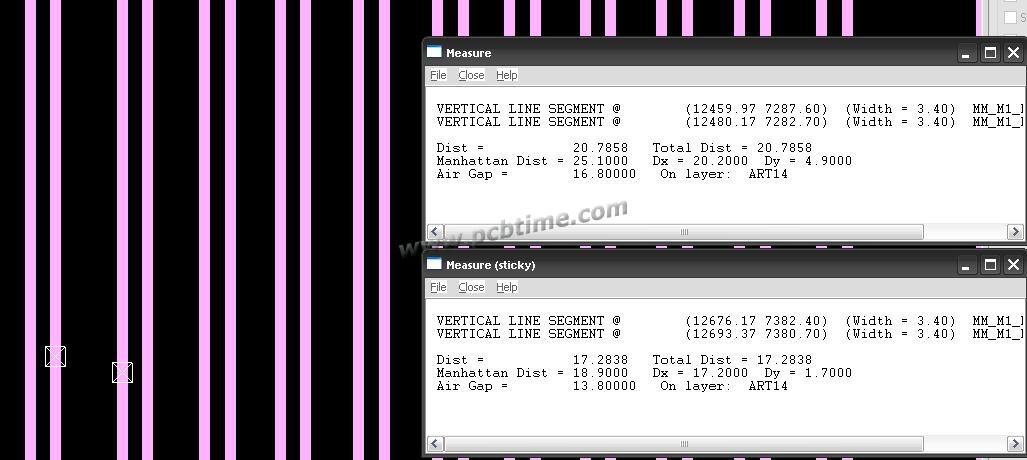

在我们设计中,往往会碰到高速信号,类似PCIE ,QPI,DMI等等,这些信号往往是十几二十跟作为一组,在我们设计的时候,有些时候差分的空气间距是没有空间来做到4W的,那么问题来了,在做不到4W的范围内,比如3.4/4.4mil的差分线,常规最少做到20mil,但是为了缩短长度,或者空间不够等等因素,做不到20,客户给的极限是10MIL(客户方面确认10MIL仿真可行),那么我们做的时候肯定规则设置是10,在做极限的时候,空间肯定是会多出来,那么我们是否需要将这些多余的空间均匀的分配,间距均匀能带来什么好处呢?

相对减少窜扰,但是我们平行的线段很长,这方面也是有一定窜扰的。并且相邻两层之间的信号最好不要做到重合平行。

刚看到,先帮顶顶 再说

要顶起,

我觉得这到没有什么特别高深的道理,均匀的意义在于让整体间距都尽可能实现最大,不让某些间距特别小。

以本例来说,如果可以做到所有的间距都是12mil,就比有的做10mil,有的做14mil更保险,毕竟对于间距宽的我们不担心,越宽越好。容易出问题的就是间距小的,虽然经过仿真,也不妨碍我们做的更保守呢,是吧

我觉得差分之间还是间距大些比较好,毕竟像楼上说的减小信号间的串扰。

按了极限值走了,多出的地方还是均匀分配比较好。有一致性。

所有的间距问题,都可以理解为做电梯问题,2个坐电梯 ,4个人坐电梯,10几个人挤电梯?你觉得2-4个陌生人做电梯会10几个人挤电梯的时候间距保持一样吗?挤的时候,就算男女挨着也正常,各自也能接受,但是2-4个人的时候,你挨着试试?不骂你bT才怪