Clock信号波形分析

时间:10-02

整理:3721RD

点击:

大家好

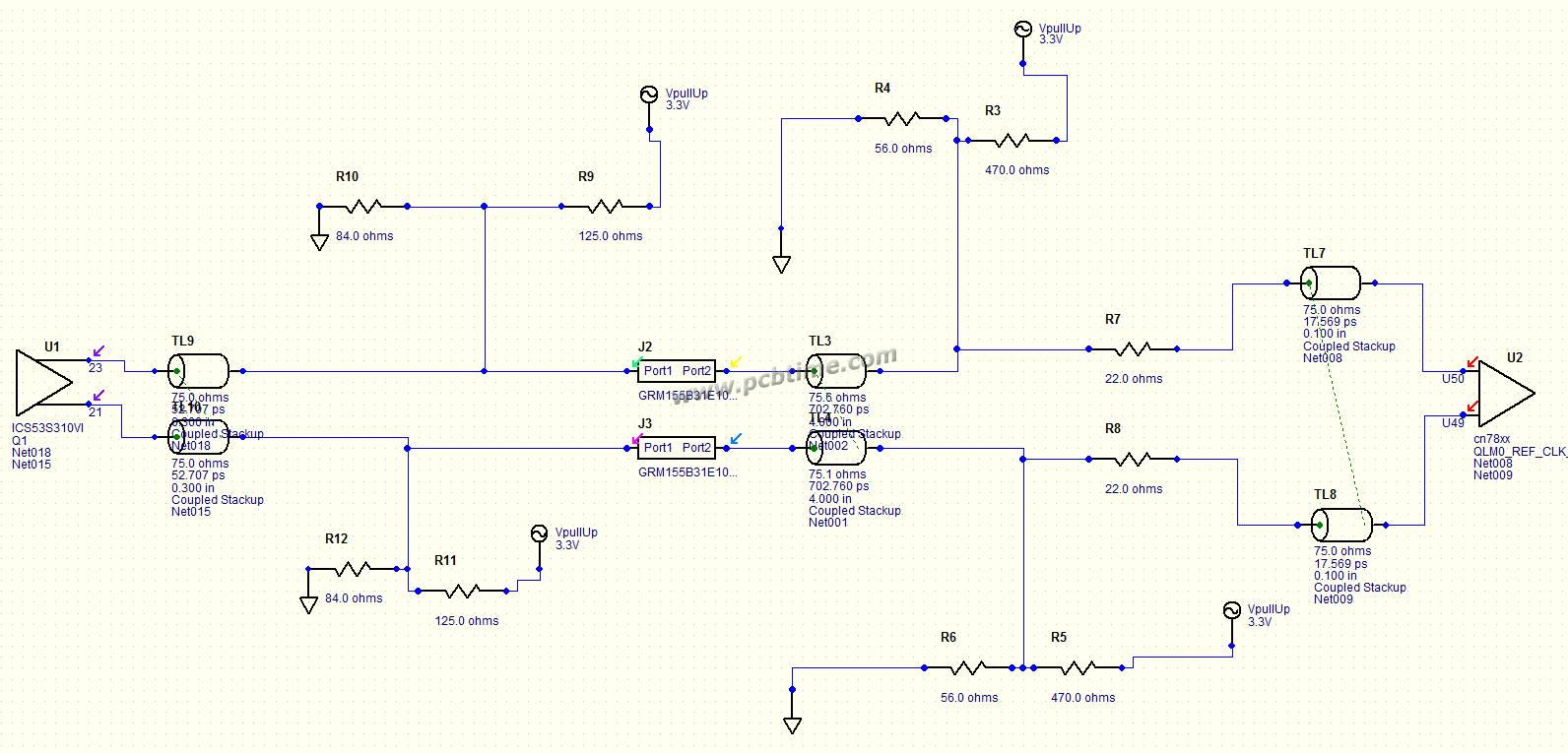

大家来讨论一下下面的CLOCK哦

输出是LVPECL电平,输入没有明确说明

中间有一个AC耦合电容

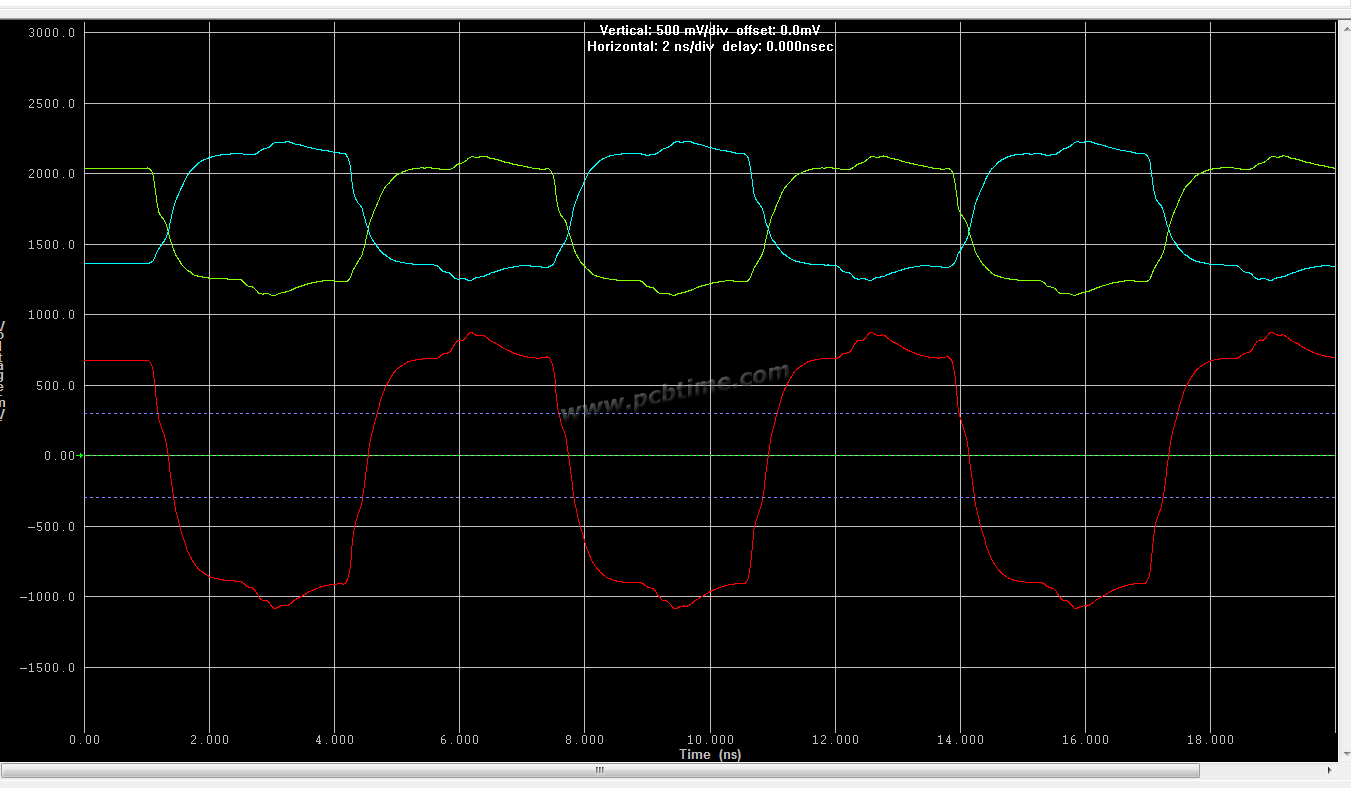

那么输入端的电平幅度为什么还这么高?

Waveform

记得不是很清楚了,以前AD这块的时钟就是采用LVPECL电平的,末端好像是有100欧姆的电阻跨接的,时钟线的差分阻抗怎么到了140作用?

差分阻抗100 ohm, 紧耦合的线

哦。这个就不知道了,以前在AD这里,也遇到同样的问题,电平的峰峰值总是超出手册的要求,小编解决了这个问题也告诉我一下,谢谢

这个电平高吗?你用的上下拉到3.3V,那么中间电平就是1.65V,你可以看到你的单端信号的交叉点就在那附近啊,你说的电平高指的是哪里?

电容会充放电。看容值大小了,容值小的话是不会吧直流分量完全拉下来的。

加AC电容后可以把直流分量去掉吗?

顶起,很好的讨论!